Execution Timing

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 4-5

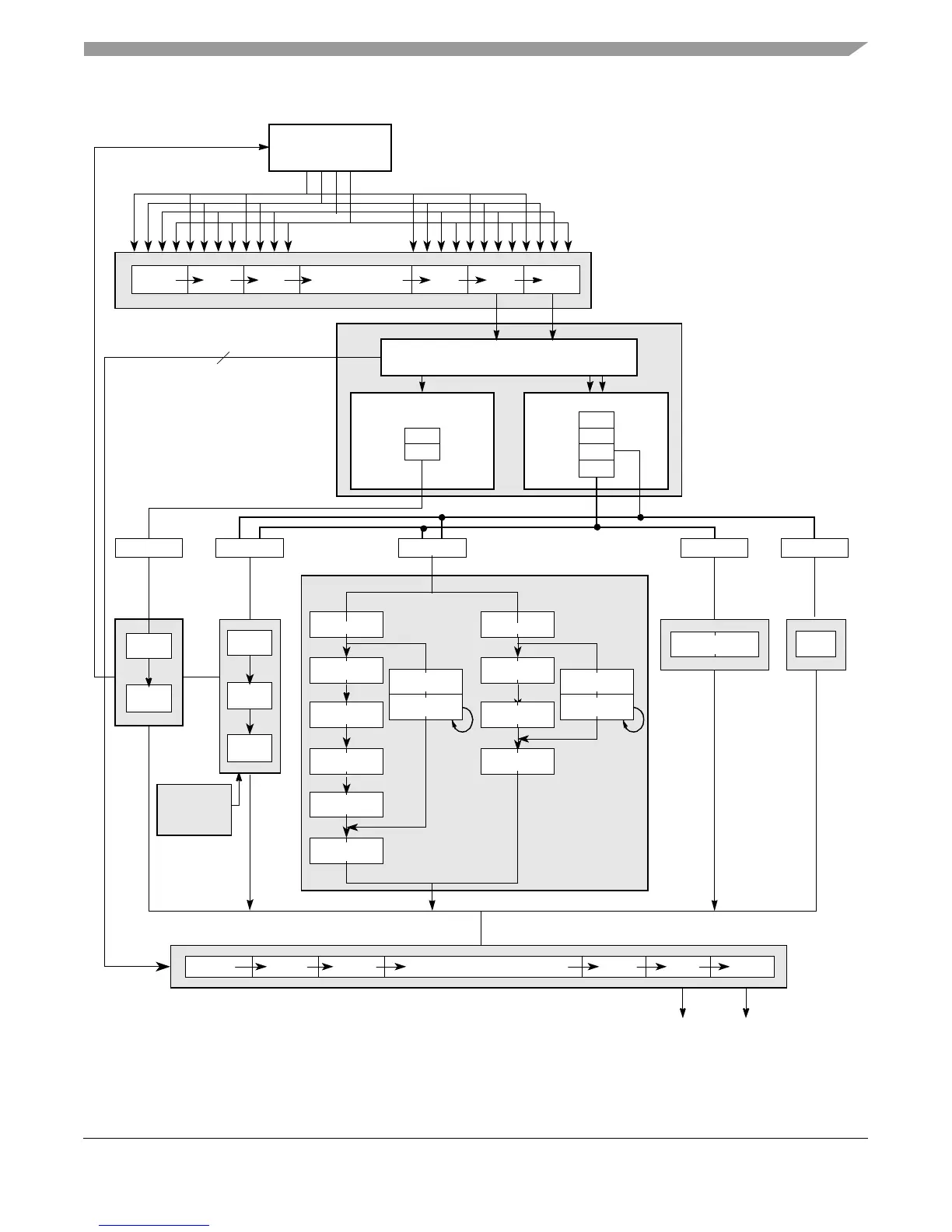

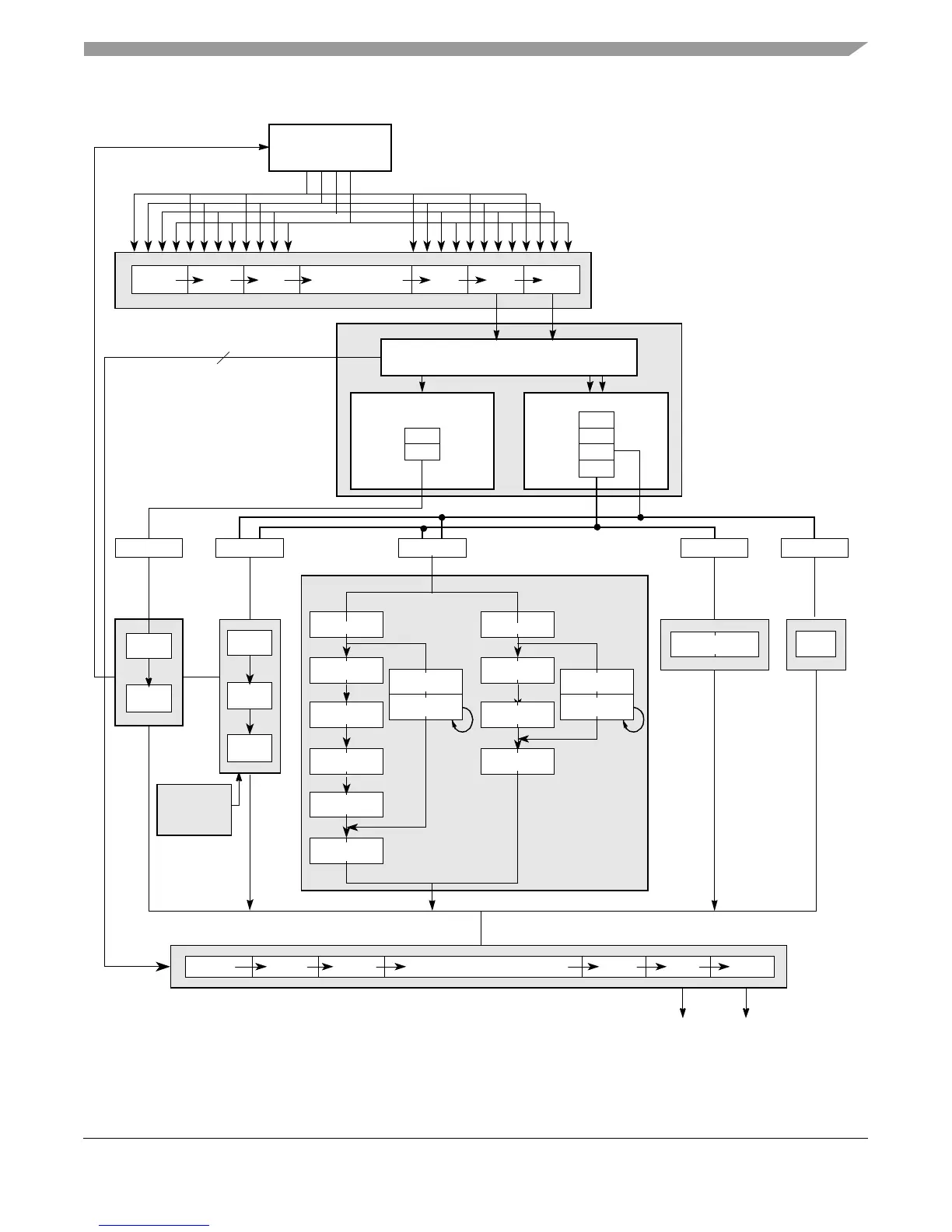

Figure 4-2. e500 Instruction Flow Diagram—Details

misprediction penalty)

(5 clocks + drain

Reservation

Stations

Upper Lower

1 or 2 instructions complete per clock cycle.

Last event in the completion stage is retirement.

Completion queue assignment

Fetch1

Fetch2/predecode

(In program order)

(Maximum four instruction every

clock cycle throughput)

Instruction

Cache

Branch Issue Queue

Decode/Dispatch

2 instructions per clock cycle

IQ9 • • • IQ2 IQ1 IQ0IQ11 IQ10

LSU-1

LSU-2

LSU-3

SU2

Signals completion queue when execution finishes

CQ13

• • • CQ1CQ2 CQ0CQ11CQ12

Completion queue (in program order)

Instruction Queue (IQ)

General Issue Queue

MU-3

MU-1

MU-4

MU-2

Upper Lower

SU1

Two instructions maximum

• • •

Maximum two

instructions issued

1 instruction issued from

BIQ per clock cycle

GIQ0

GIQ1

GIQ2

GIQ3

BIQ1

BIQ0

from GIQ per clock

cycle

Divide

Divide

Predivide

Load/Store

Queues

BU-1

BU-2

Bypass

MU-3

MU-1

MU-4

MU-2

Divide

Divide

Predivide

Bypass

MU-5

MU-6

Double Prrecision

Loading...

Loading...