PowerPC e500 Core Family Reference Manual, Rev. 1

3-20 Freescale Semiconductor

Instruction Model

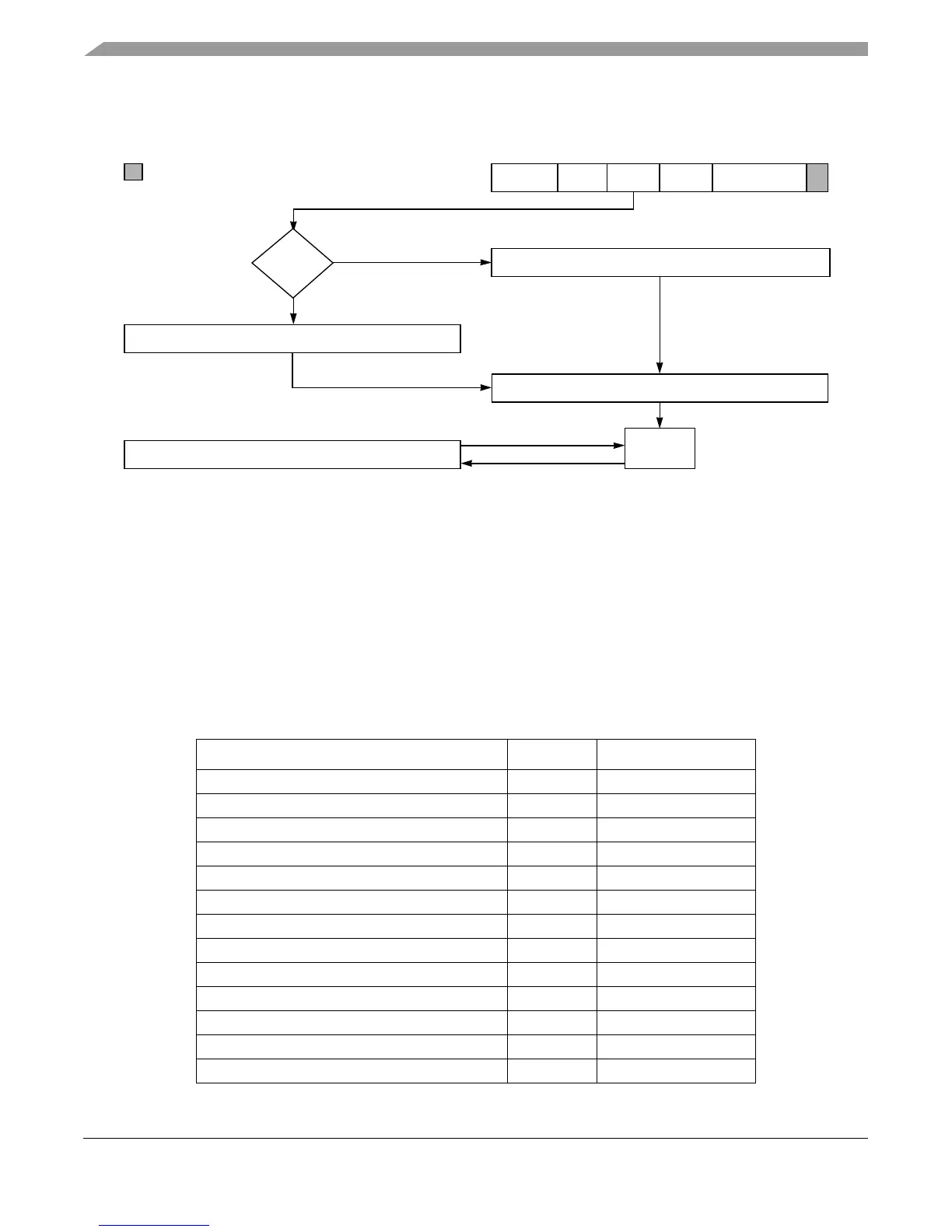

Figure 3-3 shows how an effective address is generated using register indirect addressing.

Figure 3-3. Register Indirect Addressing for Integer Loads/Stores

The instruction model chapter in the EREF describes effective address calculation. Note that in

some implementations, operations that are not naturally aligned can suffer performance

degradation. Section 5.7.6, “Alignment Interrupt,” for additional information about load and store

address alignment interrupts.

3.3.1.2.3 Integer Load Instructions

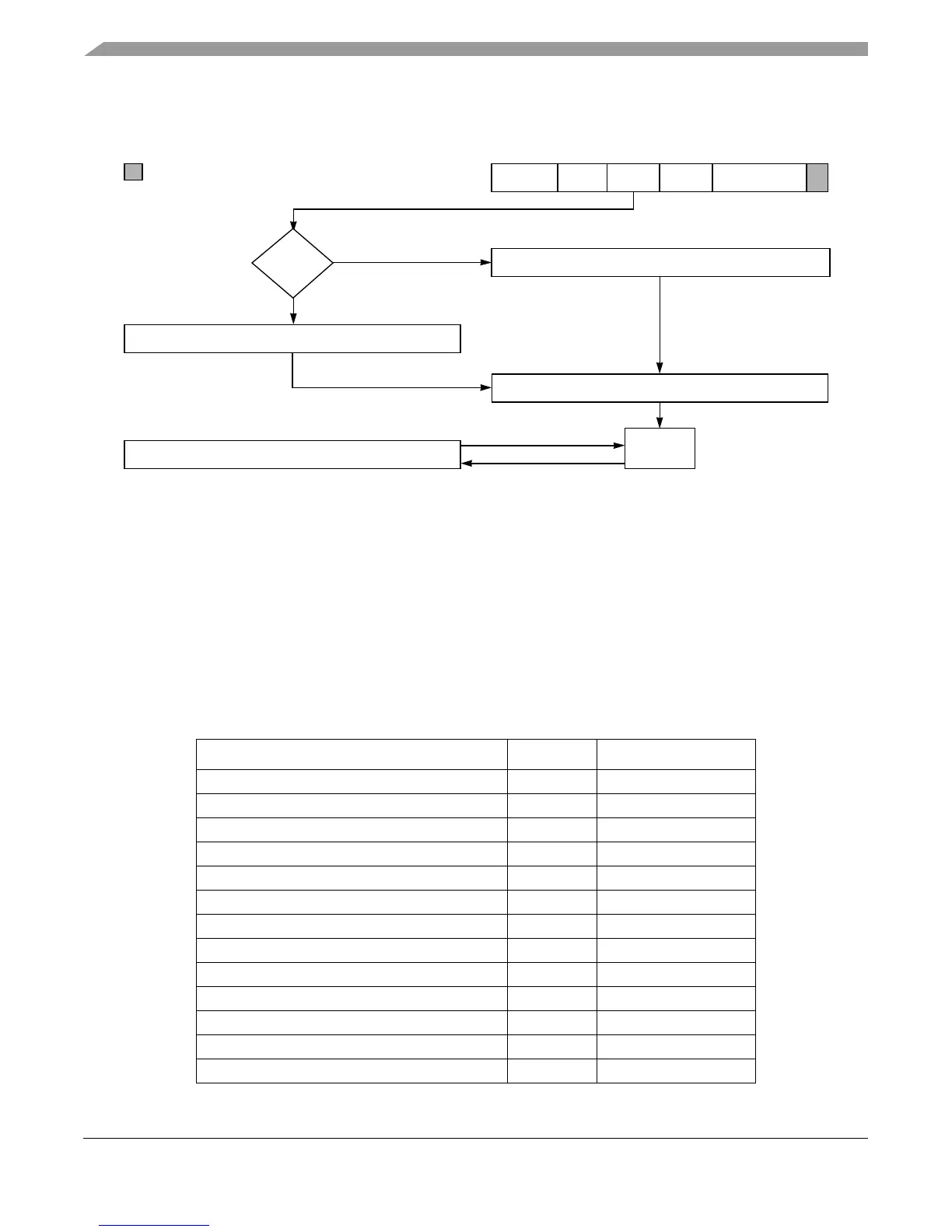

Table 3-11 summarizes the integer load instructions.

Table 3-11. Integer Load Instructions

Name Mnemonic Syntax

Load Byte and Zero lbz rD,d(rA)

Load Byte and Zero Indexed lbzx rD,rA,rB

Load Byte and Zero with Update lbzu rD,d(rA)

Load Byte and Zero with Update Indexed lbzux rD,rA,rB

Load Half Word and Zero lhz rD,d(rA)

Load Half Word and Zero Indexed lhzx rD,rA,rB

Load Half Word and Zero with Update lhzu rD,d(rA)

Load Half Word and Zero with Update Indexed lhzux rD,rA,rB

Load Half Word Algebraic lha rD,d(rA)

Load Half Word Algebraic Indexed lhax rD,rA,rB

Load Half Word Algebraic with Update lhau rD,d(rA)

Load Half Word Algebraic with Update Indexed lhaux rD,rA,rB

Load Word and Zero lwz rD,d(rA)

No

Store

Load

Ye s

0 31

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Instruction Encoding:

056101115162021 3031

rA=0?

32 63

GPR (rA)

031

Effective Address

Opcode rD/rS rA NB Subopcode 0

32 63

GPR (rD/rS)

Memory

Interface

Reserved

Loading...

Loading...