PowerPC e500 Core Family Reference Manual, Rev. 1

2-58 Freescale Semiconductor

Register Model

2.15.8 User Performance Monitor Counter Registers

(UPMC0–UPMC3)

The contents of PMC0–PMC3 are reflected to UPMC0–UPMC3, which are read by user-level

software with the mfpmr instruction using the PMR numbers in Table 2-37.

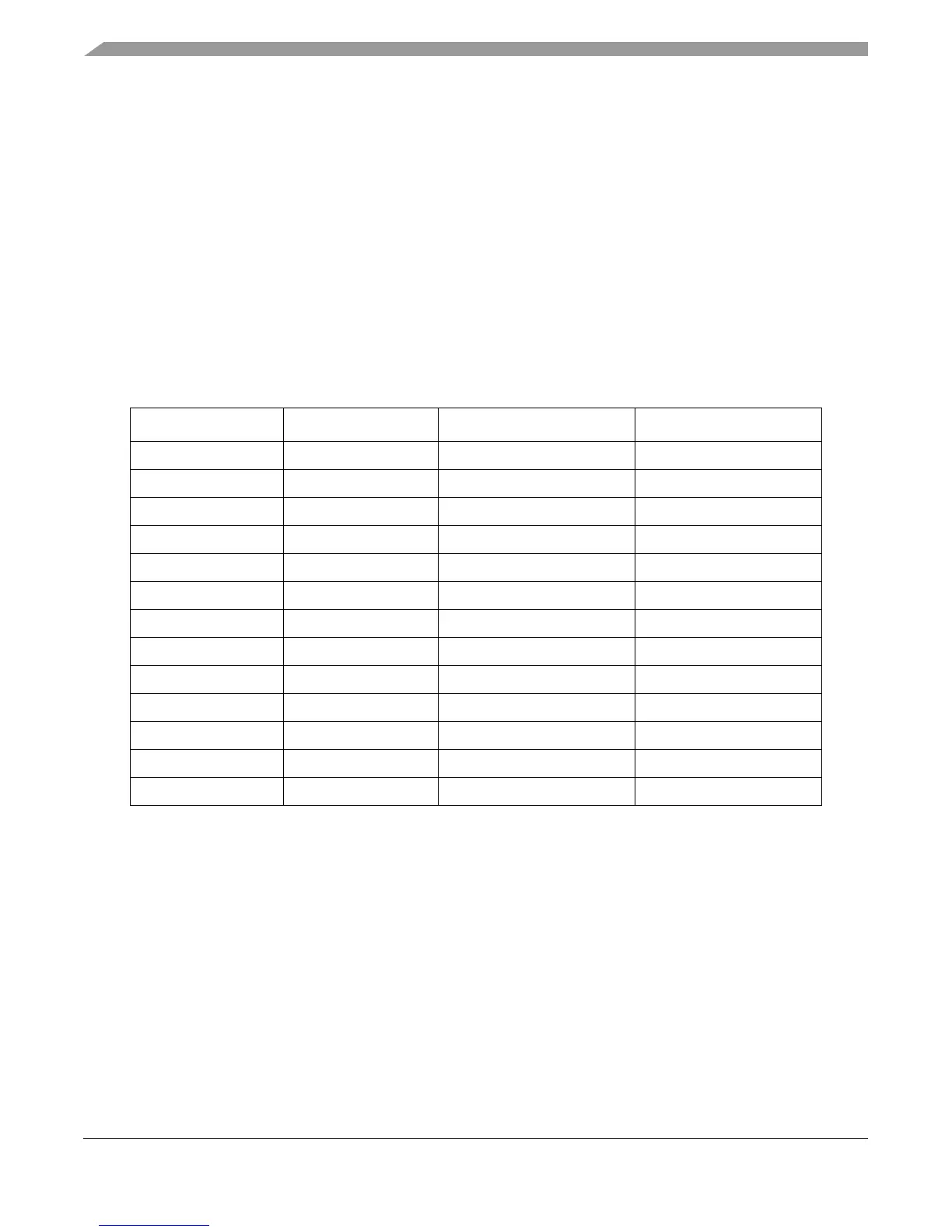

2.16 Synchronization Requirements for SPRs

Synchronization requirements for accessing certain SPRs are shown in Table 2-42. Except for

these SPRs, there are no synchronization requirements for accessing SPRs beyond those stated in

Book E.

Table 2-42. Synchronization Requirements for SPRs

Registers Instruction Instruction Required Before Instruction Required After

BBEAR mtspr bbear None isync

BBTAR mtspr bbtar None isync

BUCSR mtspr bucsr None isync

DBCR0 mtspr dbcr0 None isync

DBCR1 mtspr dbcr1 None isync

HID0 mtspr hid0 None isync

HID1 mtspr hid1 None isync

L1CSR0 mtspr l1csr0 msync, isync isync

L1CSR1 mtspr l1csr1 None isync

MAS[0-4,6] mtspr mas[0–4,6] None isync

MMUCSR0 mtspr mmucsr0 None isync

PID0–PID2 mtspr pid[0–2] None isync

SPEFSCR mtspr spefscr None isync

Loading...

Loading...