Core Complex Overview

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 1-9

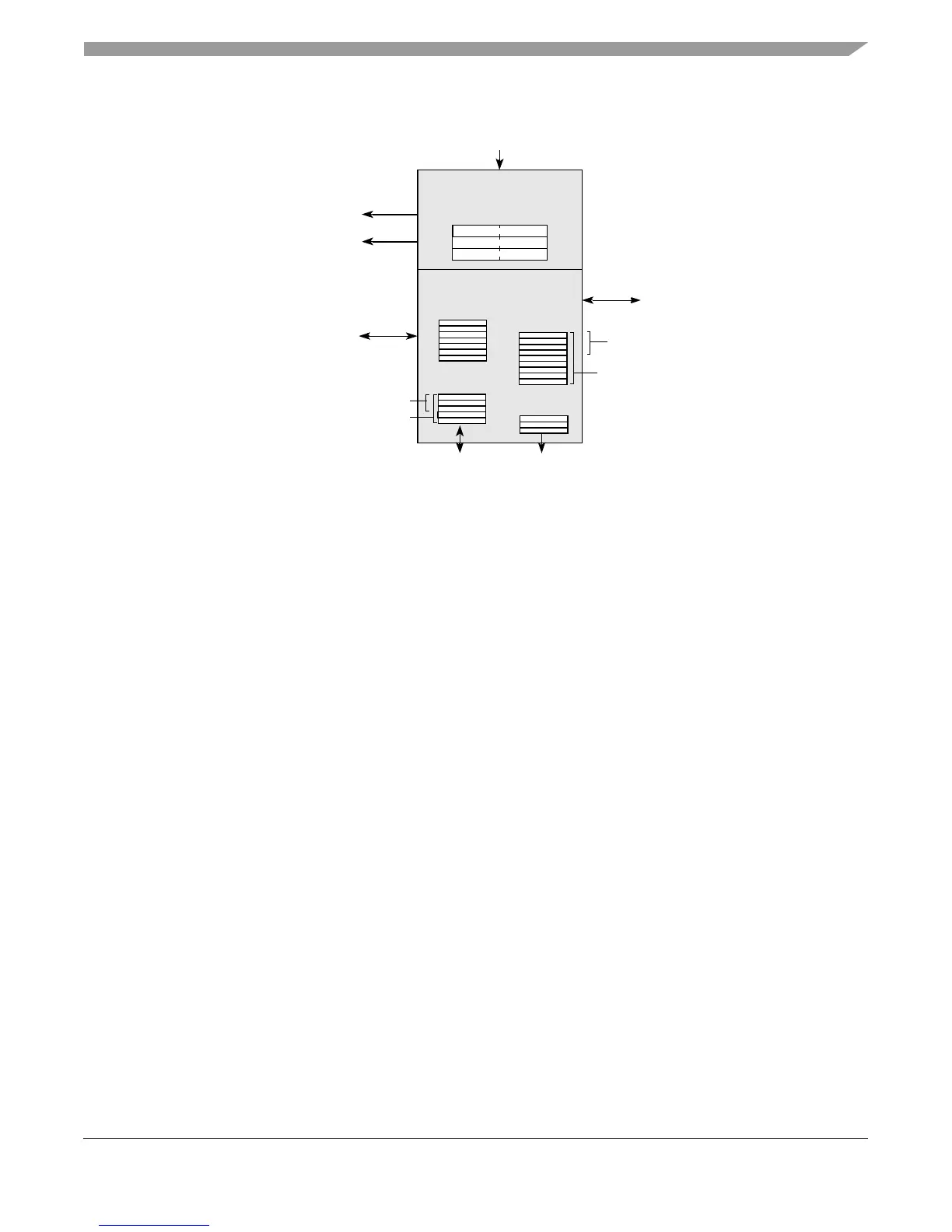

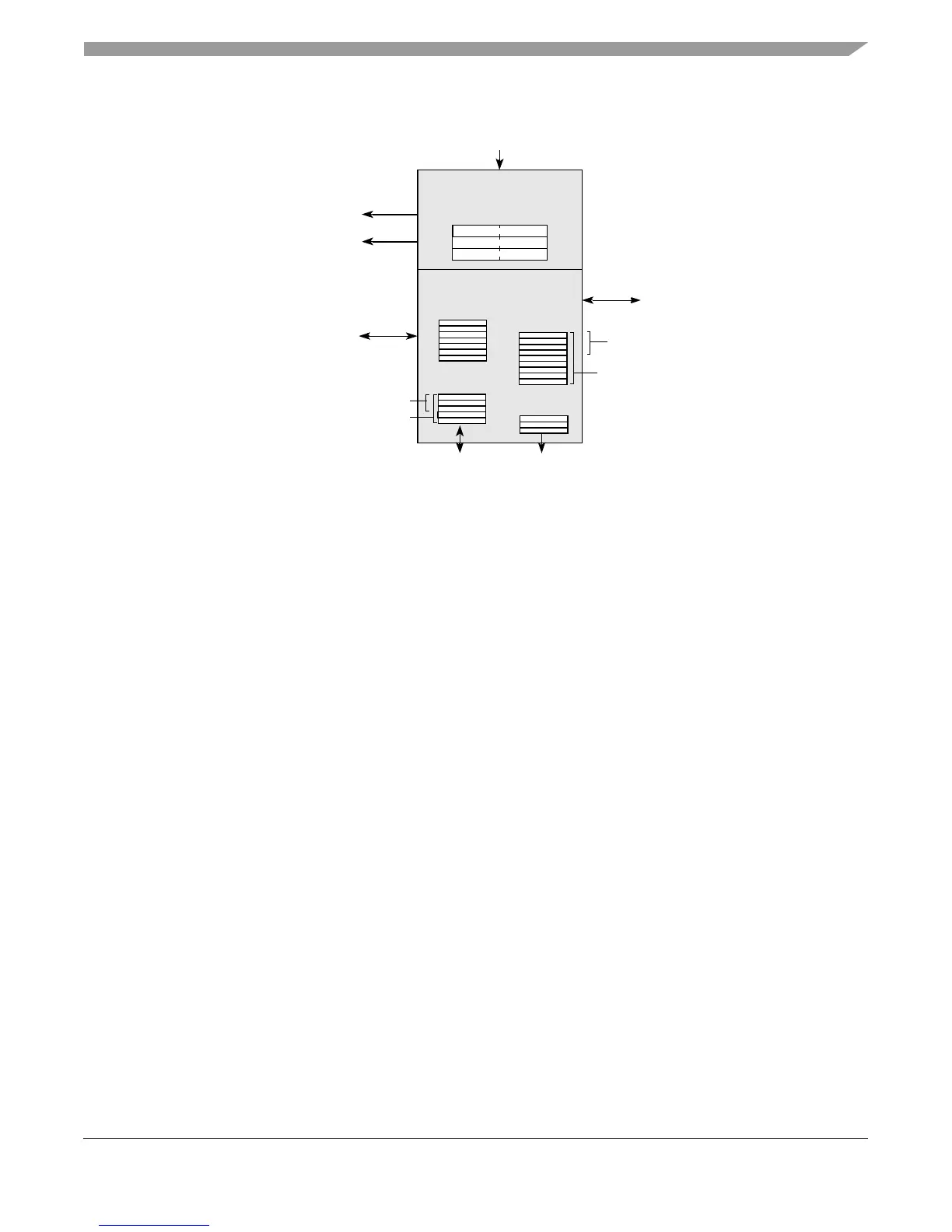

Figure 1-4. Three-Stage Load/Store Unit

— The three-entry data line fill buffer (five-entry on the e500v2) is used for loads and

cacheable stores. Stores are allocated here so loads can access data from the store

immediately.

— The data write buffer contains three entries: one dedicated for snoop pushes, one

dedicated for castouts, and one that can be used for snoop pushes or cast outs.

• Cache coherency

— Supports four-state cache coherency: modified-exclusive, exclusive, shared, and invalid

(MESI). Note, however that shared state may not be accessible in some

implementations.

— Bus support for hardware-enforced coherency (bus snooping)

• Core complex bus (CCB)—internal bus

— High-speed, on-chip local bus with data tagging

— 32-bit address bus

— Address protocol with address pipelining and retry/copyback derived from bus used by

previous generations of PowerPC processors (referred to as the 60x bus)

— Two general-purpose read data buses and one write data bus

• Extended exception handling

— Supports Book E interrupt model

– Less than 10-cycle interrupt latency

– Interrupt vector prefix register (IVPR)

Reservation

Station

Load/Store Unit

(64-/32-Bit)

Load

Data Line

Fill Buffer

Data Write

Buffer

L1 Store

Queue Miss

Queue

To core interface unit

To data cache

To GPR operand bus

To completion queue

To G P R s

Three-Stage Pipeline

Queues and Buffers

e500v2 (9 entry)

e500v1 (3 entry)

e500v2 (5 entry)

e500v1 (4 entry)

Loading...

Loading...