Instruction Model

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 3-25

Note that the e500 implements the Integer Select instruction, isel, which can be used to more

efficiently handle sequences with multiple conditional branches. Its syntax is given in

Section 3.8.2, “Integer Select (isel) APU.” A detailed description including an example of how isel

can be used can be found in the APUs chapter of the EREF.

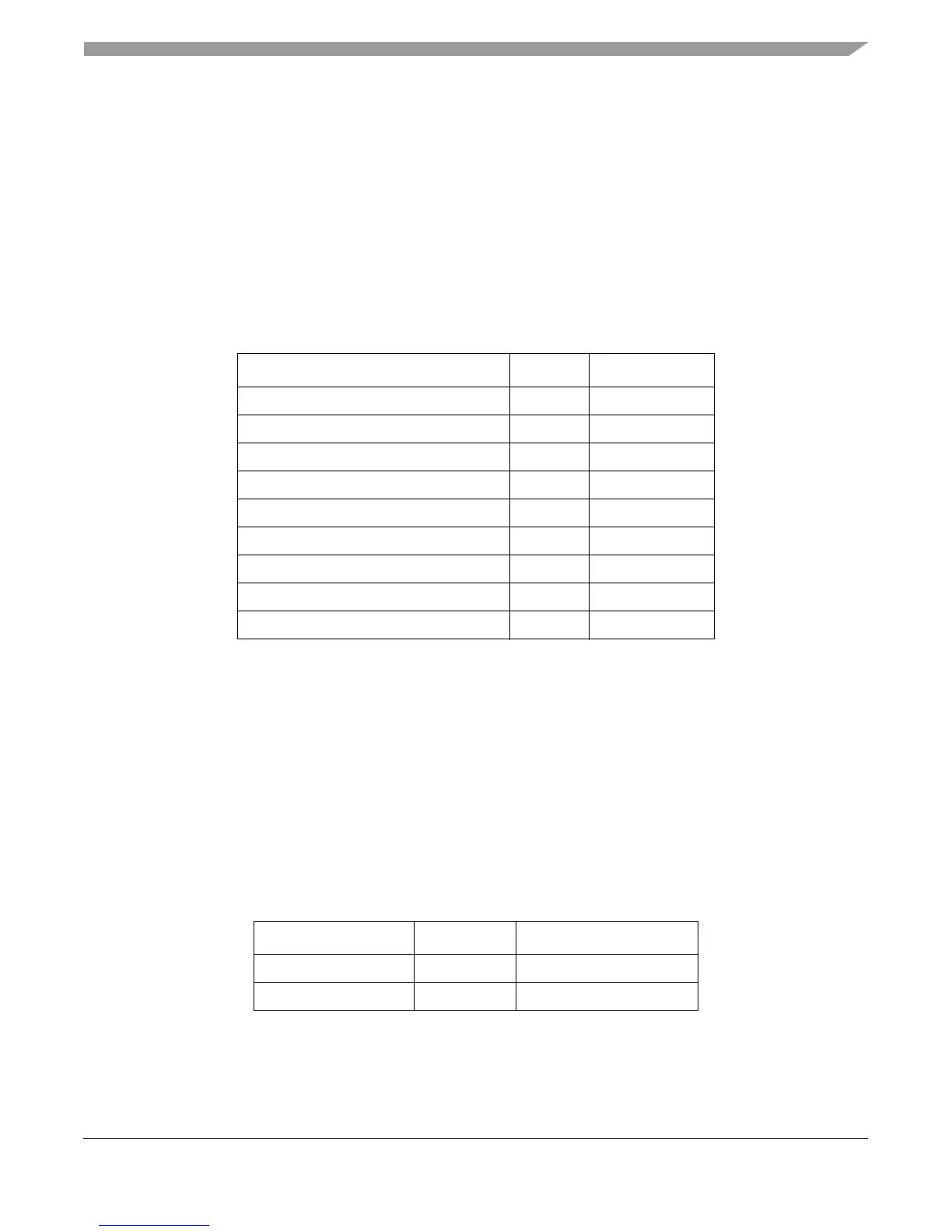

3.3.1.3.3 Condition Register Logical Instructions

CR logical instructions, shown in Table 3-18, and the Move Condition Register Field (mcrf)

instruction are also defined as flow control instructions.

Note that if the LR update option is enabled for any of these instructions, the Book E architecture

defines these forms of the instructions as invalid.

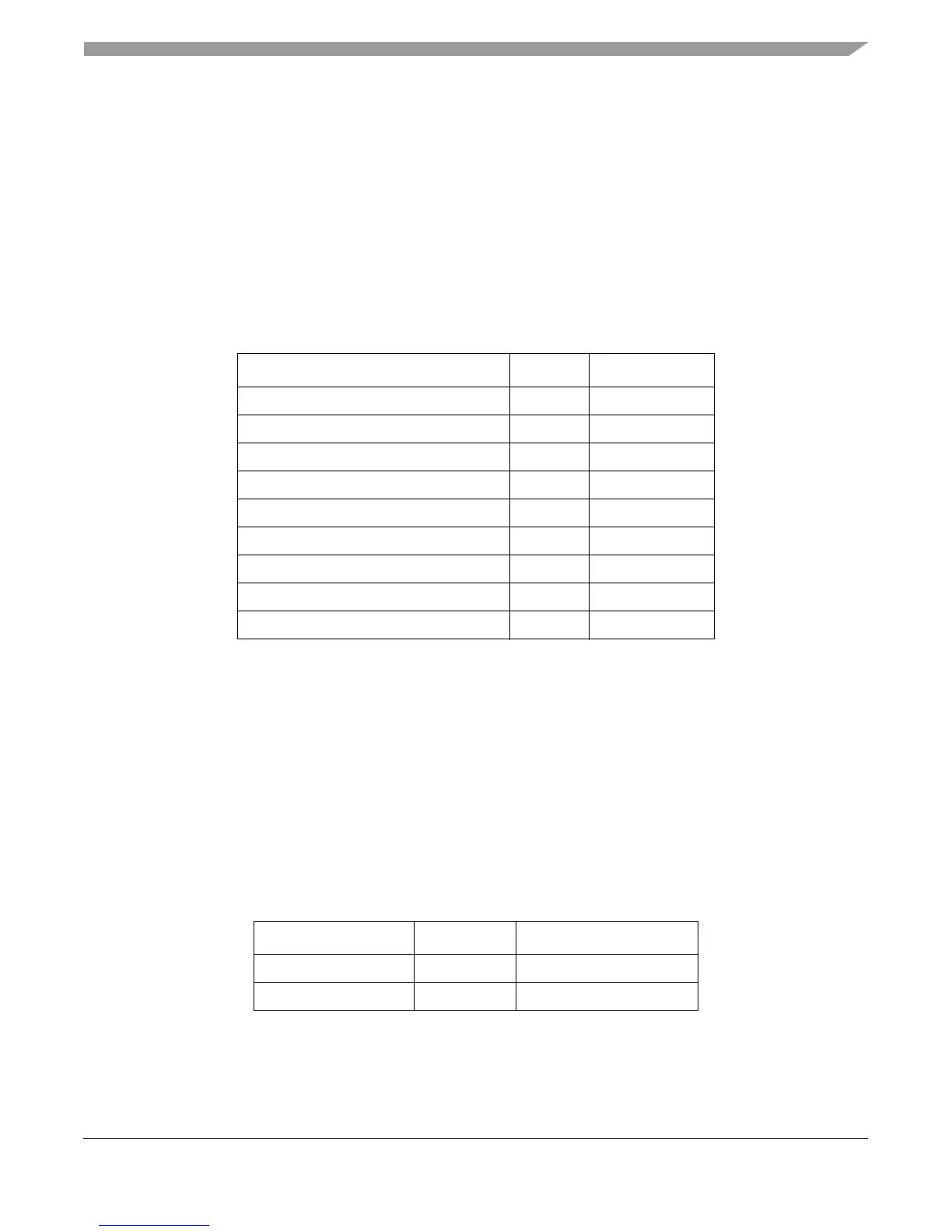

3.3.1.3.4 Trap Instructions

The trap instructions shown in Table 3-19 test for a specified set of conditions. If any of the

conditions tested by a trap instruction are met, the system trap type program interrupt is taken. For

more information, see Section 5.7.7, “Program Interrupt.” If the tested conditions are not met,

instruction execution continues normally. See Appendix C, “Simplified Mnemonics for PowerPC

Instructions.”

Table 3-18. Condition Register Logical Instructions

Name Mnemonic Syntax

Condition Register AND crand crbD,crbA,crbB

Condition Register OR cror crbD,crbA,crbB

Condition Register XOR crxor crbD,crbA,crbB

Condition Register NAND crnand crbD,crbA,crbB

Condition Register NOR crnor crbD,crbA,crbB

Condition Register Equivalent creqv crbD,crbA,crbB

Condition Register AND with Complement crandc crbD,crbA,crbB

Condition Register OR with Complement crorc crbD,crbA,crbB

Move Condition Register Field mcrf crfD,crfS

Table 3-19. Trap Instructions

Name Mnemonic Syntax

Trap Word Immediate twi TO,rA,SIMM

Trap Word tw TO,rA,rB

Loading...

Loading...