PowerPC e500 Core Family Reference Manual, Rev. 1

3-60 Freescale Semiconductor

Instruction Model

3.8.2 Integer Select (isel) APU

The integer select APU consists of the isel instruction, a conditional register move that helps

eliminate branches. Further information about isel may be found in the APUs chapter of the EREF.

3.8.3 Performance Monitor APU

The e500 core complex implements a performance monitor as an APU. Software communication

with the performance monitor APU is achieved through performance monitor registers (PMRs)

rather than SPRs. New instructions are provided to move to and from these PMRs. Performance

monitor APU instructions are described in Table 3-39. Full descriptions of these instructions can

be found in the EREF chapter, “Instruction Set.”

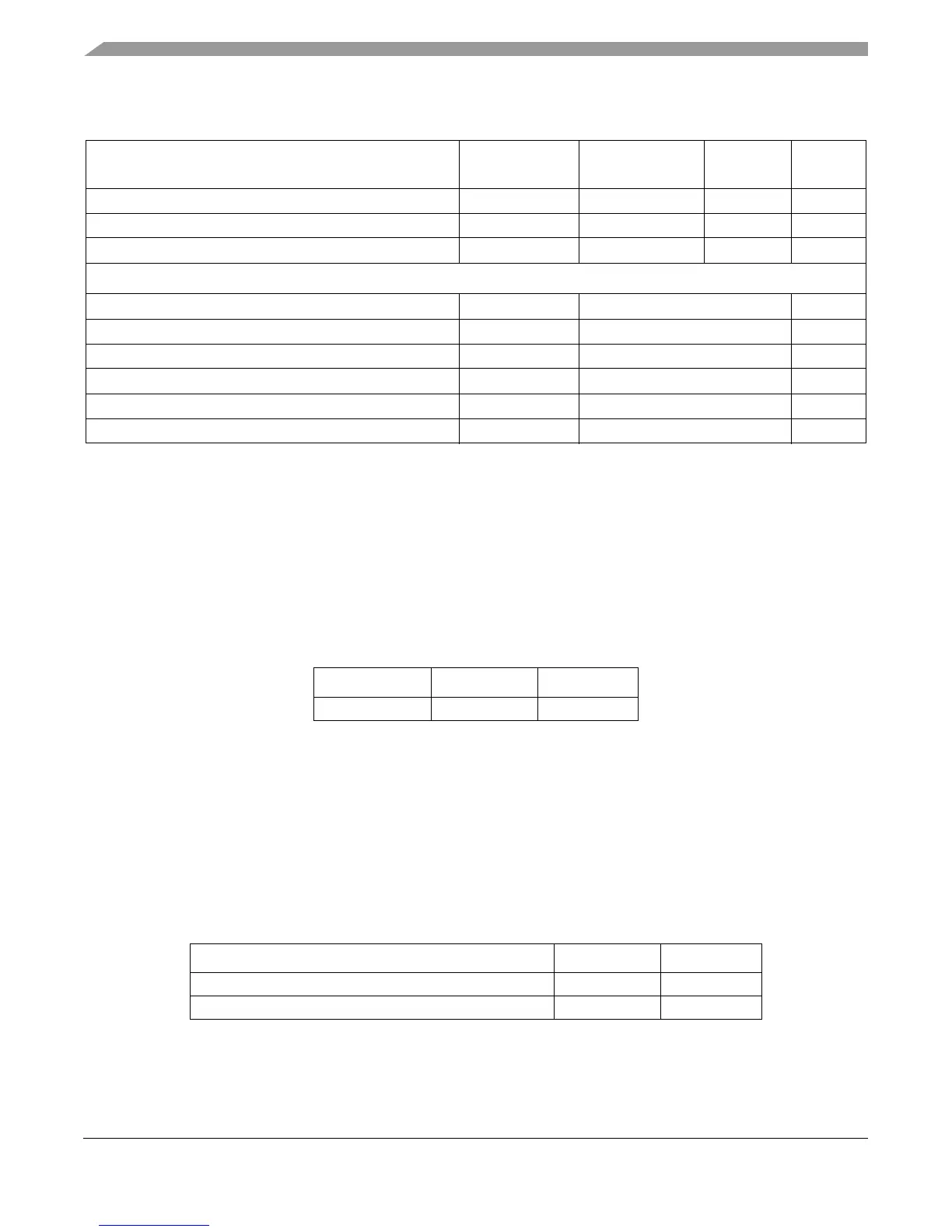

Floating-Point Test Equal efststeq efdtsteq evfststeq crD,rA,rB

Floating-Point Test Greater Than efststgt efdtstgt evfststgt crD,rA,rB

Floating-Point Test Less Than efststlt efdtstlt evfststlt crD,rA,rB

SPE Double Word Load/Store Instructions

Vector Load Double Word into Double Word — evldd rD,d(rA)

Vector Load Double Word into Double Word Indexed — evlddx rD,rA,rB

Vector Merge High — evmergehi rD,rA,rB

Vector Merge Low — evmergelo rD,rA,rB

Vector Store Double of Double — evstdd rS,d(rA)

Vector Store Double of Double Indexed — evstddx rS,rA,rB

Note: on e500v1, floating-point operations that produce a result of zero may generate an incorrect sign.

1

Exception detection for these instructions is implementation dependent. On the e500, Infinities, NaNs, and Denorms are

always be treated as Norms. No exceptions are taken if SPEFSCR[FINVE] = 1.

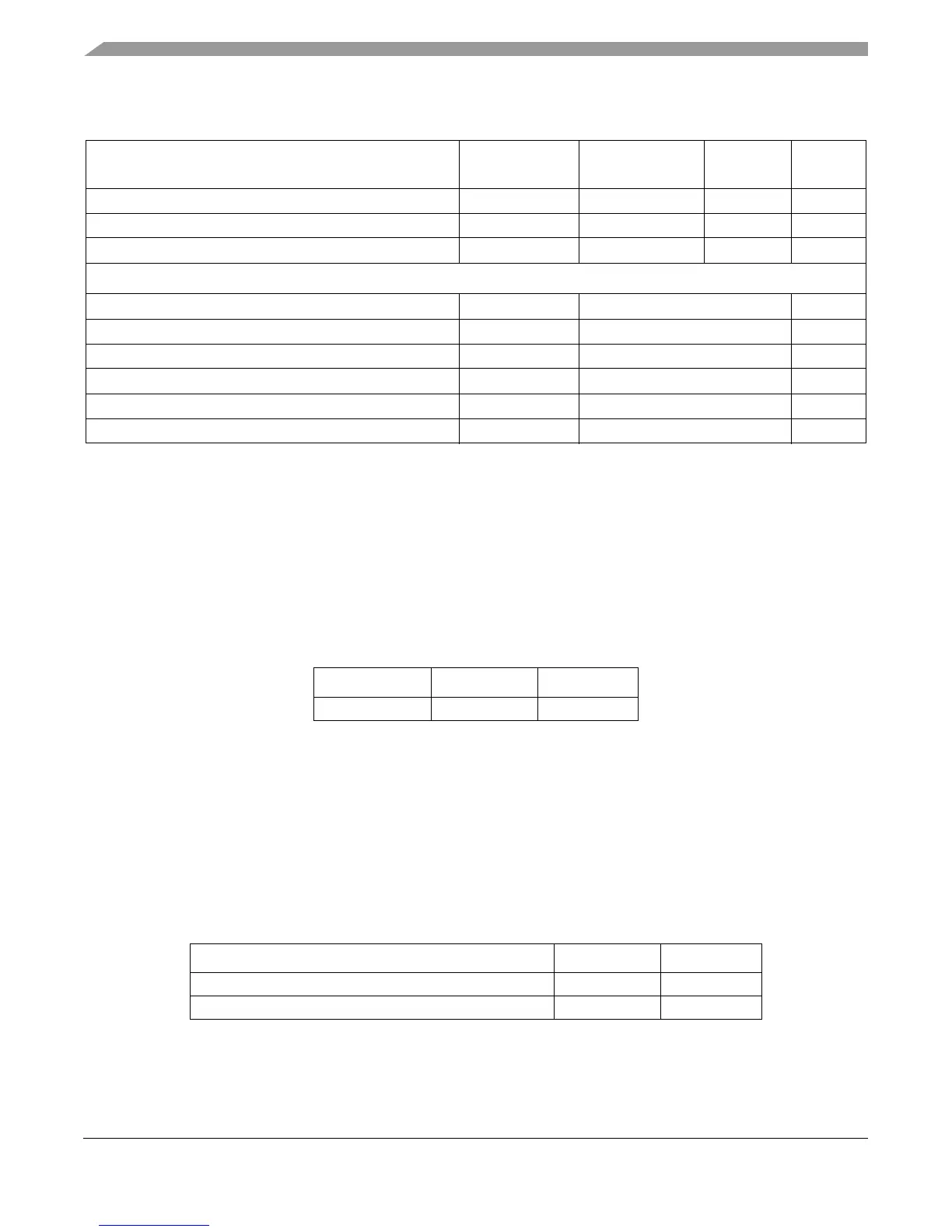

Table 3-38. Integer Select APU Instruction

Name Mnemonic Syntax

Integer Select isel rD,rA,rB,crB

Table 3-39. Performance Monitor APU Instructions

Name Mnemonic Syntax

Move from Performance Monitor Register mfpmr rD,PMRN

Move to Performance Monitor Register mtpmr PMRN,rS

Table 3-37. Vector and Scalar Floating-Point APU Instructions (continued)

Instruction

Single-Precision

Scalar

Double-Precision

Scalar (e500v2)

Vector Syntax

Loading...

Loading...