Instruction Model

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 3-59

The embedded floating-point APUs are described as follows:

• Vector SPFP instructions operate on a vector of two 32-bit, single-precision floating-point

numbers that reside in the upper and lower halves of the 64-bit GPRs.

• Scalar SPFP instructions operate on single 32-bit operands that reside in the lower 32-bits

of the GPRs.

• Scalar DPFP instructions (e500v2 only) operate on single 64-bit operands that reside in the

64-bit GPRs. Full descriptions of these instructions is provided in Section 10.4,

“Double-Precision Floating-Point APU (e500 v2 Only).”

These instructions are listed in Table 3-37.

NOTE

Vector and scalar versions of the instructions have the same syntax.

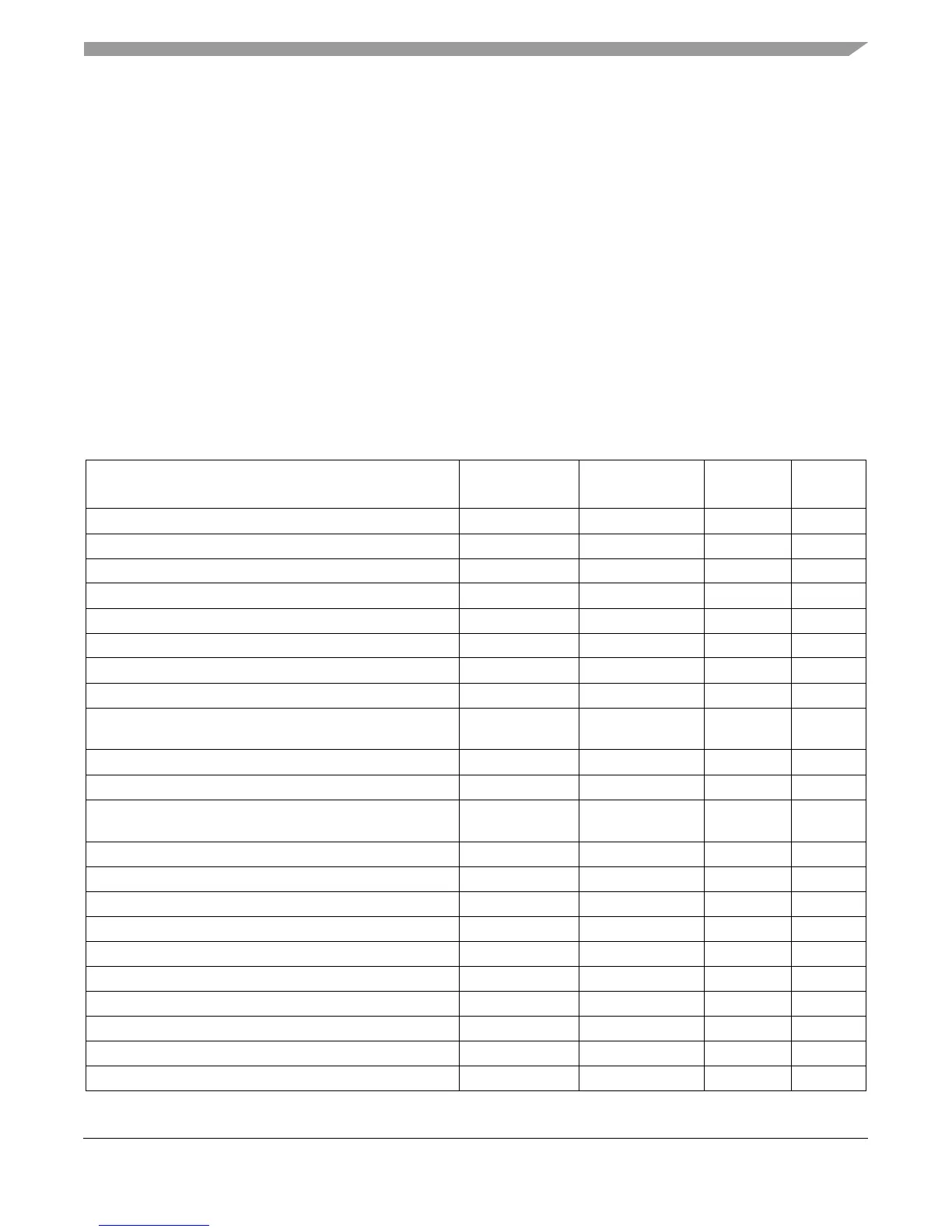

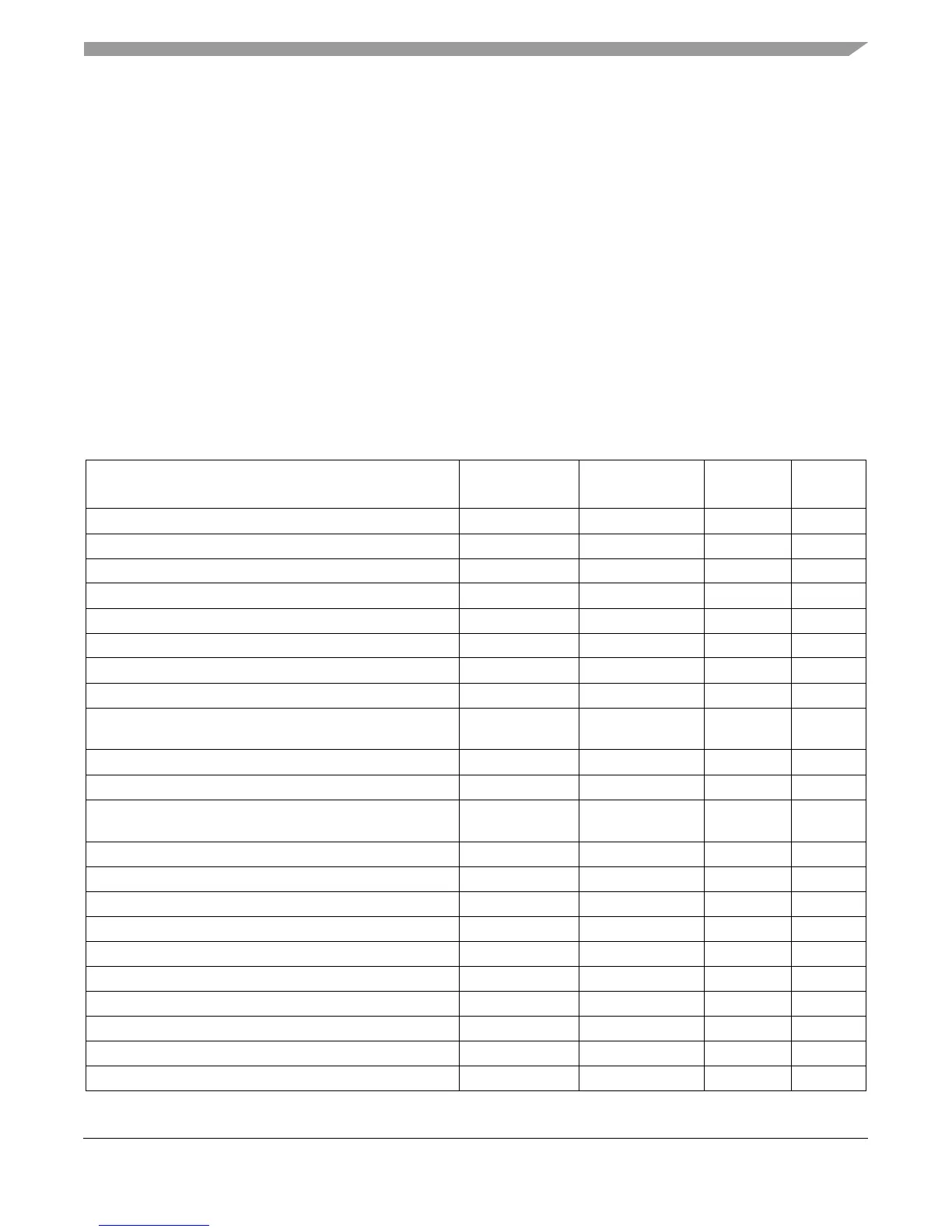

Table 3-37. Vector and Scalar Floating-Point APU Instructions

Instruction

Single-Precision

Scalar

Double-Precision

Scalar (e500v2)

Vector Syntax

Convert Floating-Point Double- from Single-Precision —efdcfs—rD,rB

Convert Floating-Point from Signed Fraction efscfsf efdcfsf evfscfsf rD,rB

Convert Floating-Point from Signed Integer efscfsi efdcfsi evfscfsi rD,rB

Convert Floating-Point from Unsigned Fraction efscfuf efdcfuf evfscfuf rD,rB

Convert Floating-Point from Unsigned Integer efscfui efdcfui evfscfui rD,rB

Convert Floating-Point Single- from Double-Precision —efscfd—rD,rB

Convert Floating-Point to Signed Fraction efsctsf efdctsf evfsctsf rD,rB

Convert Floating-Point to Signed Integer efsctsi efdctsi evfsctsi rD,rB

Convert Floating-Point to Signed Integer with Round toward

Zero

efsctsiz efdctsiz evfsctsiz rD,rB

Convert Floating-Point to Unsigned Fraction efsctuf efdctuf evfsctuf rD,rB

Convert Floating-Point to Unsigned Integer efsctui efdctui evfsctui rD,rB

Convert Floating-Point to Unsigned Integer with Round

toward Zero

efsctuiz efdctuiz evfsctuiz rD,rB

Floating-Point Absolute Value efsabs

1

efdabs evfsabs rD,rA

Floating-Point Add efsadd efdadd evfsadd rD,rA,rB

Floating-Point Compare Equal efscmpeq efdcmpeq evfscmpeq crD,rA,rB

Floating-Point Compare Greater Than efscmpgt efdcmpgt evfscmpgt crD,rA,rB

Floating-Point Compare Less Than efscmplt efdcmplt evfscmplt crD,rA,rB

Floating-Point Divide efsdiv efddiv evfsdiv rD,rA,rB

Floating-Point Multiply efsmul efdmul evfsmul rD,rA,rB

Floating-Point Negate efsneg

1

efdneg evfsneg rD,rA

Floating-Point Negative Absolute Value efsnabs

1

efdnabs evfsnabs rD,rA

Floating-Point Subtract efssub efdsub evfssub rD,rA,rB

Loading...

Loading...