L1 Caches

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 11-11

The core complex provides full hardware support for PowerPC cache coherency and ordering

instructions and full hardware implementation of the TLB management instructions.

The core complex broadcasts cache management instructions (dcbst, dcblc (CT = 1), icblc

(CT = 1), dcbf, dcbi, mbar, msync, tlbsync, icbi) only if the address broadcast enable bit

(HID1[ABE]) is set. On some implementations, ABE must be set to allow management of external

L2 caches.

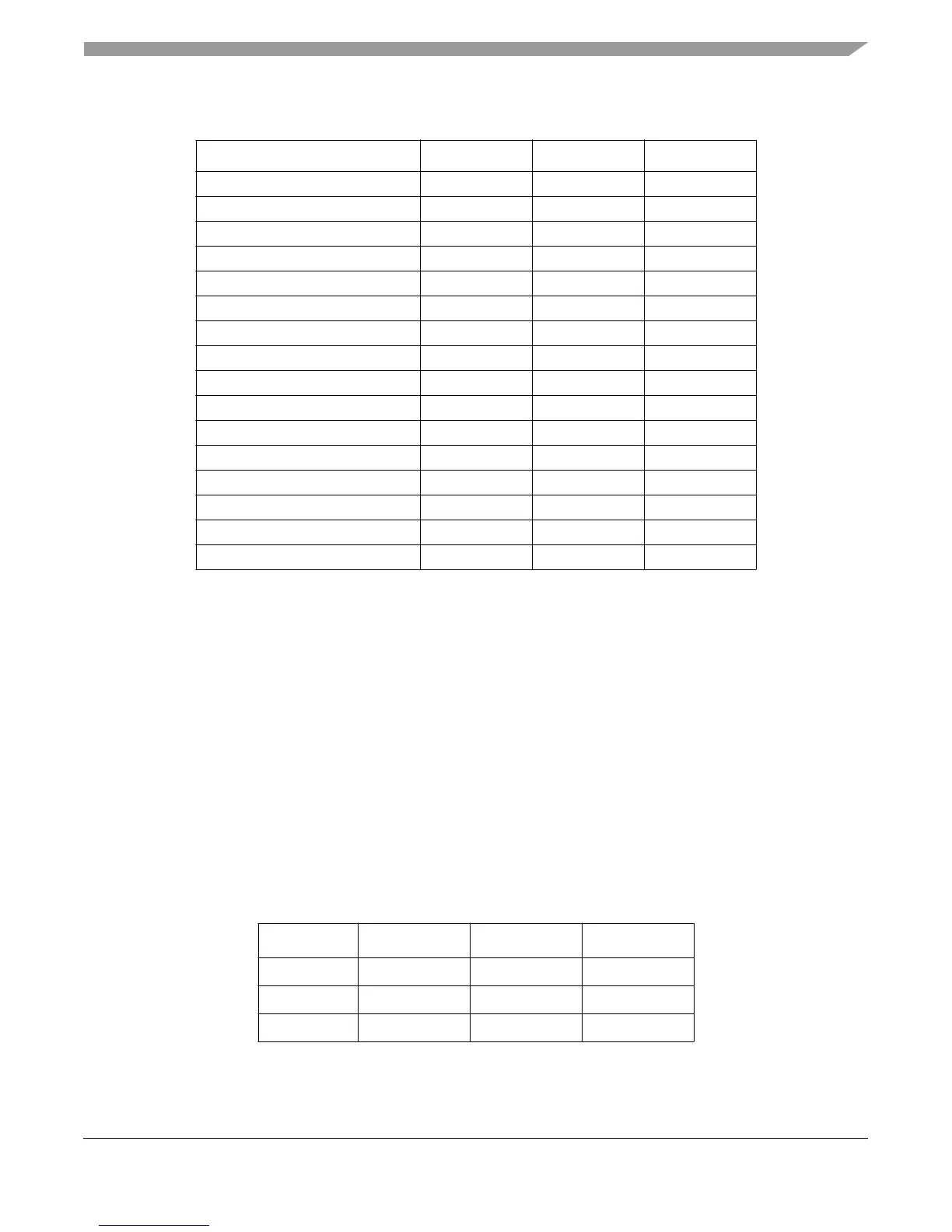

11.3.2 Instruction Cache Coherency Model

The instruction cache supports only invalid and valid state. Table 11-3 describes how execution of

instruction cache control instructions affect L1 instruction cache coherency states.

dcbtstls (CT = 1) 00x Any I

dcbz 00x Any M

icblc (CT = 1) xxx Any same

icbt (CT = 1) x0x Any I

icbtls (CT = 1) x0x Any I

Load xxx M, E, or S same

Load x0x I S or E

Load x1x Any same

lwarx 00x M, E, or S same

lwarx 00x I S or E

lwarx 01x Any same

Store 00x Any M

Store 10x M or E same

Store 10x S or I I

Store 01x Any same

stwcx 00x Any M

1

The x indicates that the value is either 0 or 1

Table 11-3. L1 Instruction Cache Coherency State Transitions

Event WIM Initial State Final State

icbi xxx V or I I

icblc (CT = 0) xxx V or I same

icbtls (CT = 0) x01 V or I V

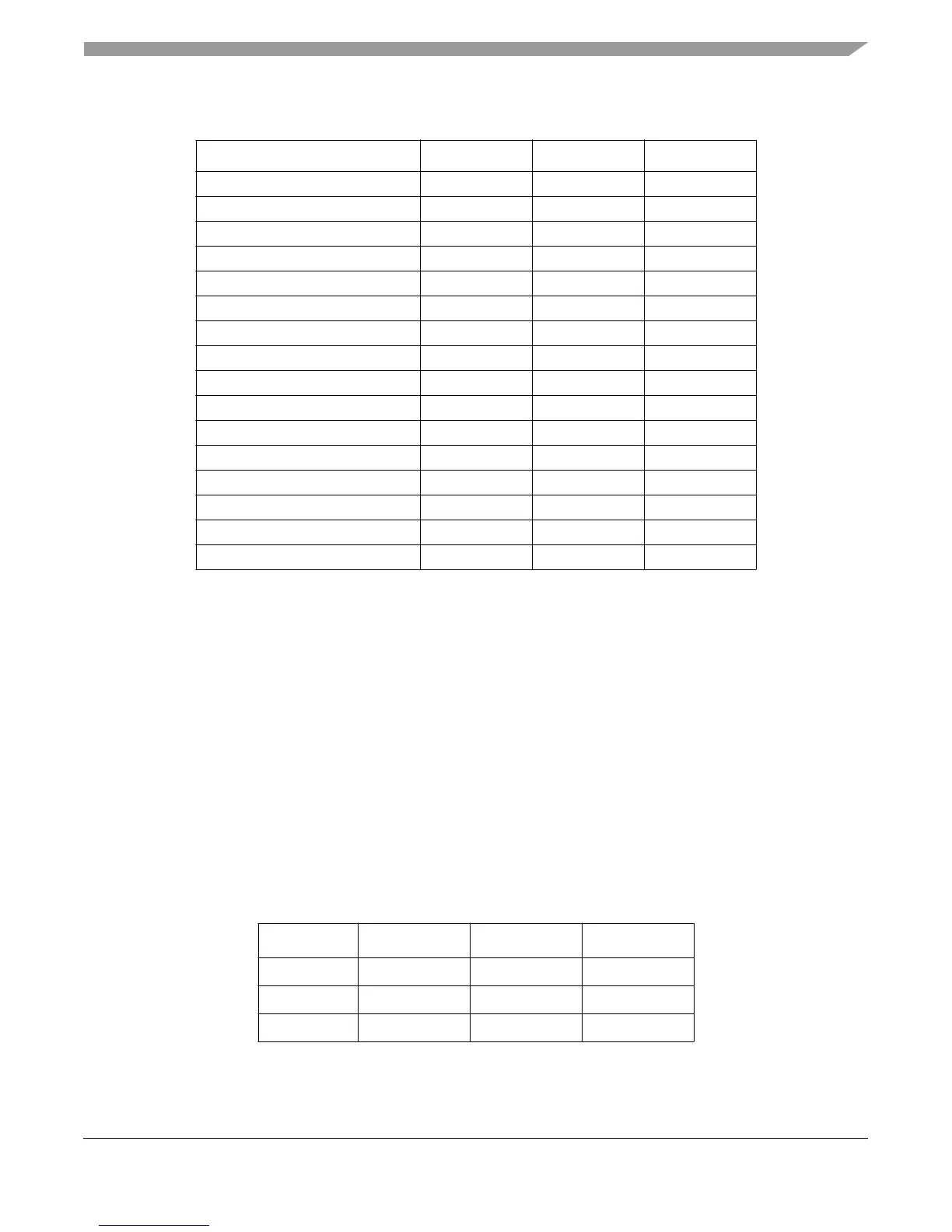

Table 11-2. L1 Data Cache Coherency State Transitions (continued)

Event WIM Initial State Final State

Loading...

Loading...