PowerPC e500 Core Family Reference Manual, Rev. 1

11-10 Freescale Semiconductor

L1 Caches

Each 32-byte data cache block contains status bits that define the MESI state of the cache line. The

core complex uses these bits to support coherency protocols and to direct reload operations.

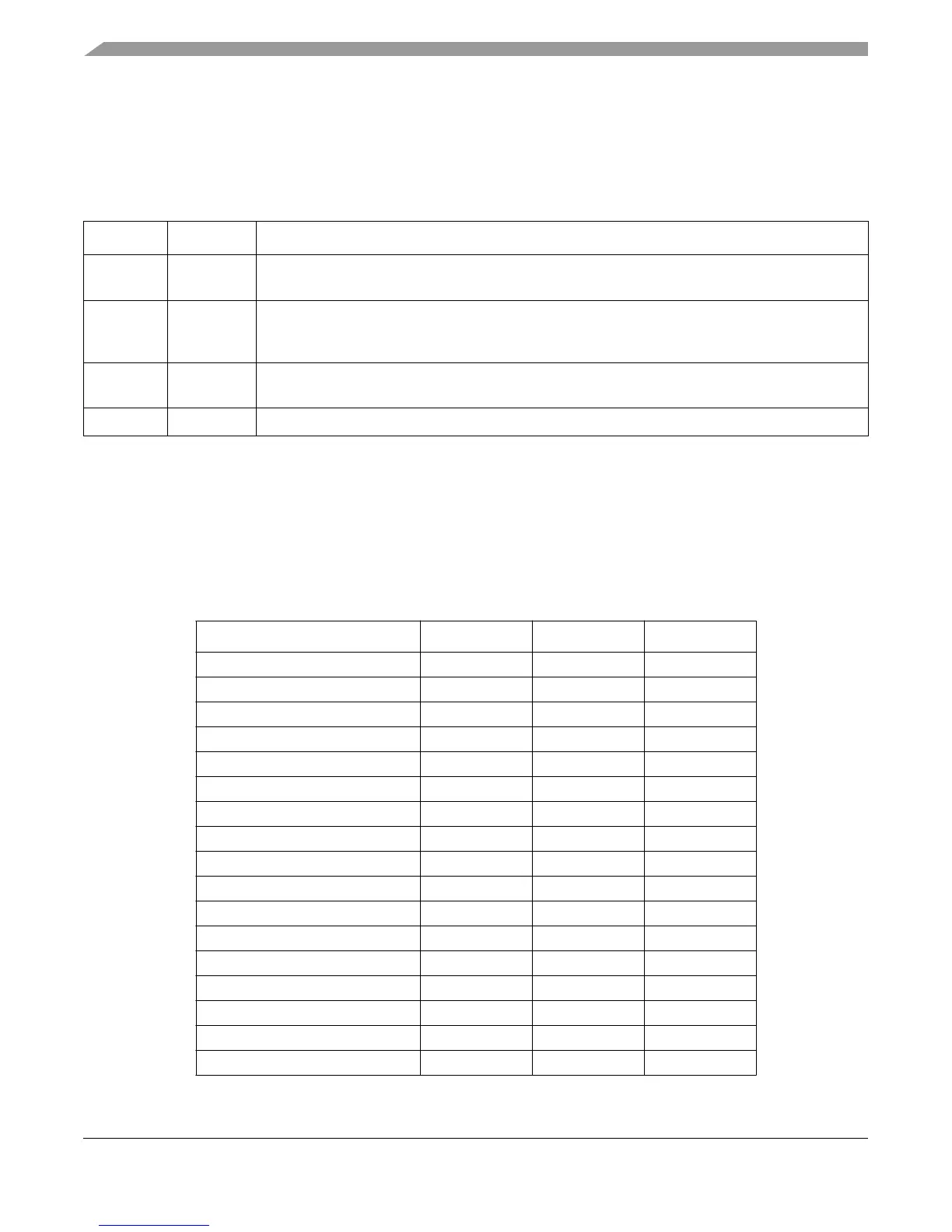

Table 11-1 describes data cache states.

Every data cache block state is defined by its status bits. Note that in a multiprocessor system, a

cache line can exist in the exclusive state in at most one L1 data cache at a time.

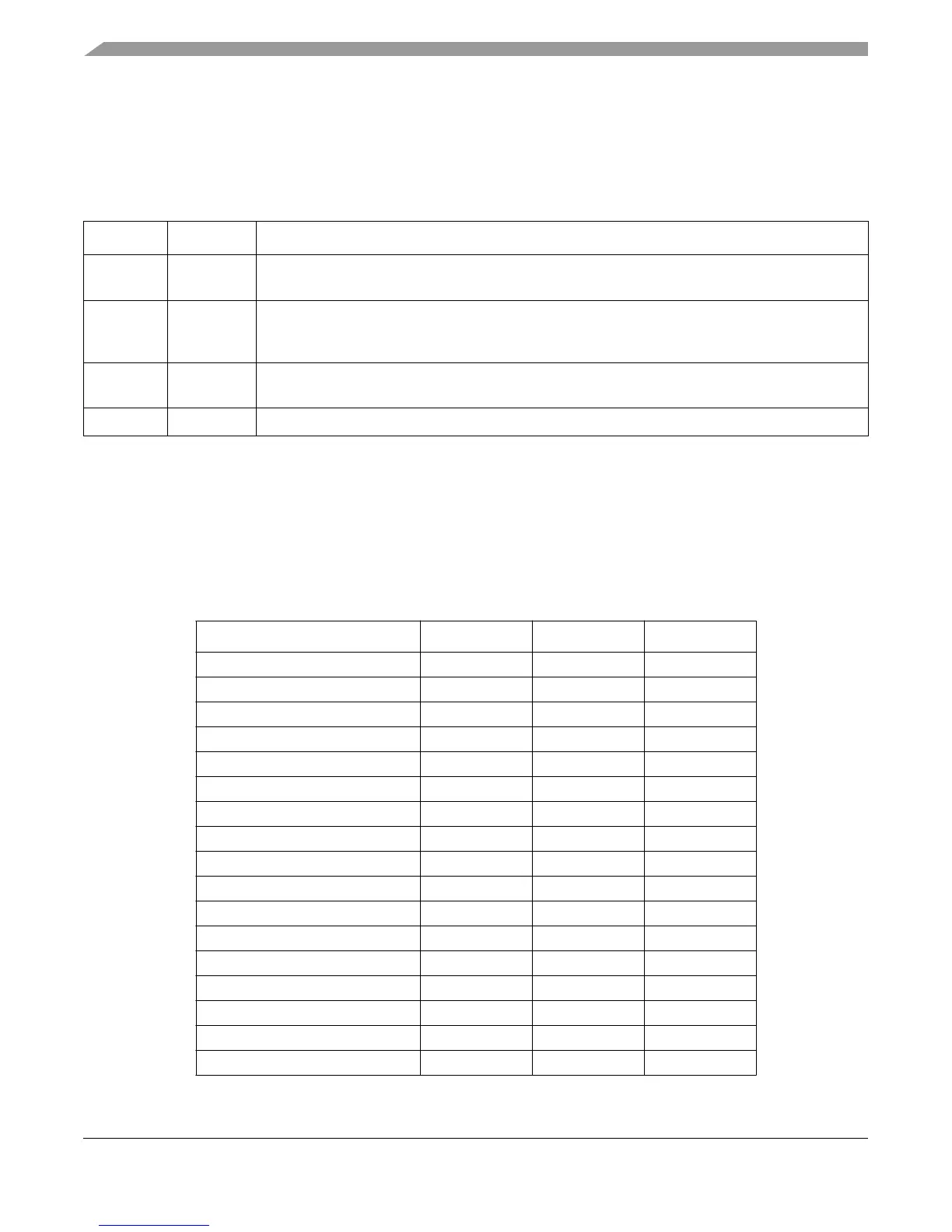

Table 11-2 describes how execution of some instructions affects L1 data cache coherency states

and WIM bit settings. For more information, see Section 11.3.4, “WIMGE Settings and Effect on

L1 Caches.”

Table 11-1. Cache Line State Definitions

Status Bits Name Description

101 Modified (M) The line is in the cache and has been modified with respect to main memory. It does not reside in

any other coherent caches.

100 Exclusive (E) The line is present in the cache, and this cache has exclusive ownership of the line. It is not present

in any other coherent cache and it is the same as main memory. This processor may subsequently

modify this line without notifying other bus masters.

110 Shared (S) The addressed line is in the cache, it may be in another coherent cache, and it is the same as main

memory. It cannot be modified by any processor.

0xx Invalid (I) The cache location does not contain valid data.

Table 11-2. L1 Data Cache Coherency State Transitions

Event WIM Initial State Final State

dcba 00x

1

Any M

dcbf xxx Any I

dcbi xxx Any I

dcblc (CT = 0) xxx Any same

dcblc (CT = 1) xxx Any same

dcbst xxx Any I

dcbt (CT = 0) x0x M, E, or S same

dcbt (CT = 0) x0x I S or E

dcbt (CT = 1) x0x Any I

dcbtls (CT = 0) x0x M, E, or S same

dcbtls (CT = 0) x0x I S or E

dcbtls (CT = 1) x0x Any I

dcbtst (CT = 0) 00x M, E, or S same

dcbtst (CT = 0) 00x I E

dcbtst (CT = 1) 00x Any I

dcbtstls (CT = 0) 00x M or E same

dcbtstls (CT = 0) 00x S or I E

Loading...

Loading...