PowerPC e500 Core Family Reference Manual, Rev. 1

1-2 Freescale Semiconductor

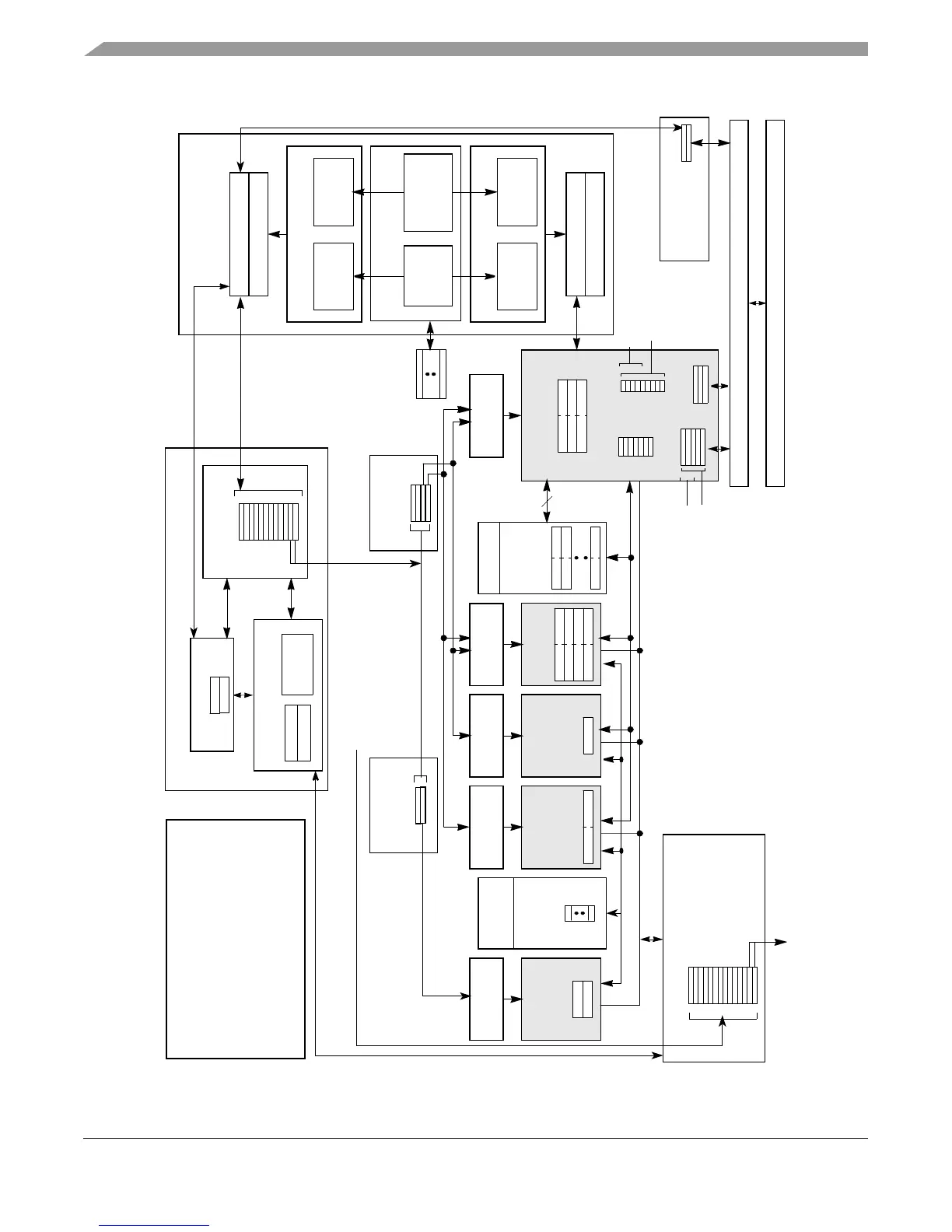

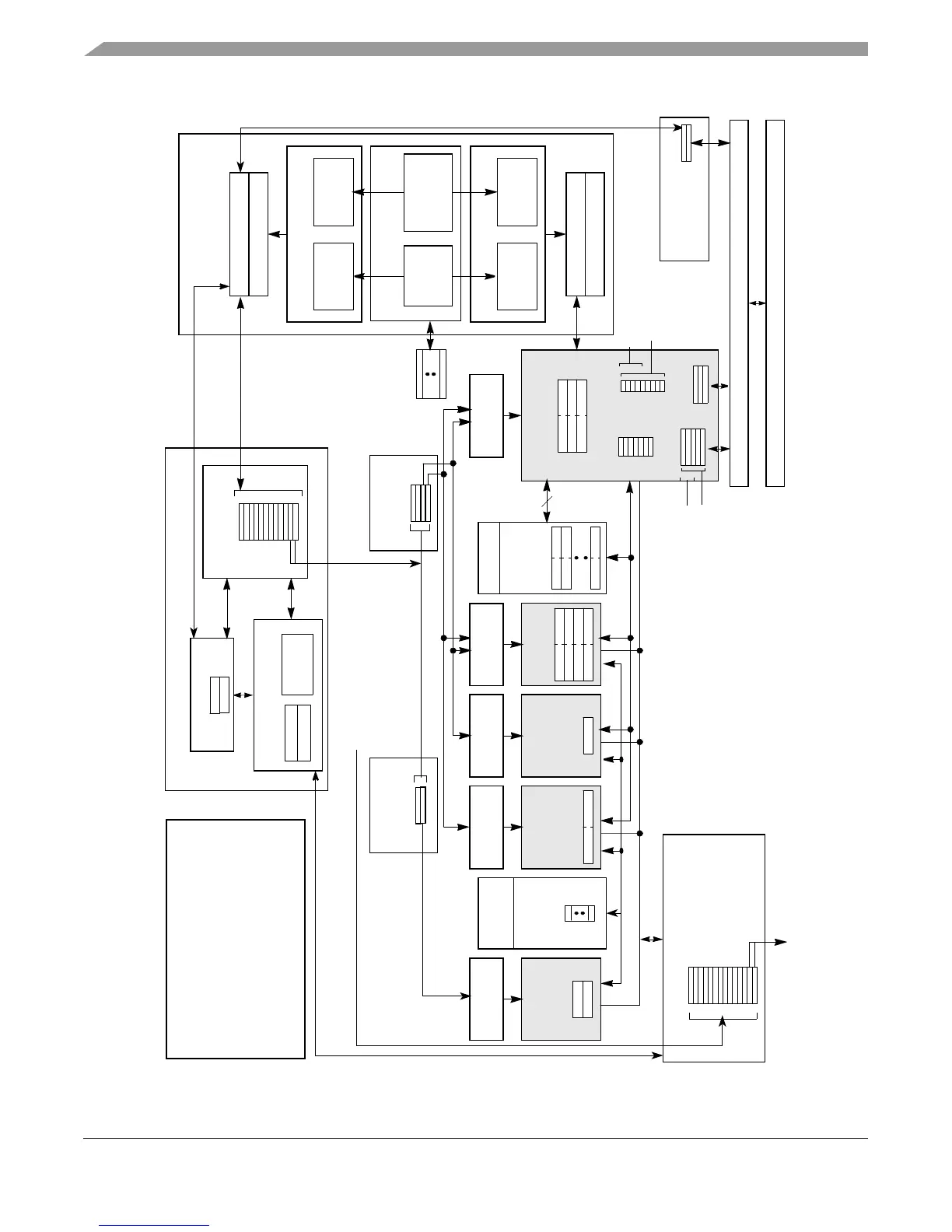

Core Complex Overview

Figure 1-1. e500 Core Complex Block Diagram

Reservation

Station

Reservation

Station

Reservation

Station

Additional Features

• Time Base Counter/Decrementer

• Clock Multiplier

• JTAG/COP Interface

• Power Management

• Performance Monitor

Fetch Stages

Branch Prediction Unit

BTB

512 Entry

CTR

LR

Instruction Unit

Instruction Queue

(12 instructions)

Program order is maintained by passing instructions

Reservation

Branch

Unit

GPR File

Completion Queue (14 Entry)

Load/Store Unit

32-/

64-Bit

L2 MMUs

256/512-Entry

TLB Array

16-Entry

Condition

CR Field

128-Bit

General Issue

Queue (GIQ)

Branch Issue

Queue (BIQ)

(TLB0)

TLB Array

(TLB1)

Register

Unified

L1 Data MMU

64-Entry

D-L1TLB4K

4-Entry

D-L1VSP

Two Instruction Dispatch

(1 BIQ, 2 GIQ)

Core Interface Unit

L1 Instruction MMU

64-Entry

I-L1TLB4K

4-Entry

I-L1VSP

32-Kbyte I Cache

Station

Reservation

Station

Simple Unit 1

(32/64 bit)

Simple Unit 2

(32 bit)

Multiple Unit

(64/32 bit)

(64/32 bit)

Memory Unit

(4 Instructions)

Tags

Tags

32-Kbyte D Cache

Maximum

MAS

Registers

Two Instructions

Retire per Cycle

from the IQ to the CQ at dispatch.

Load Miss

Data Line

Fill Buffer Data Write

Buffer

Instruction Line

Rename

Buffers (14)

Fill Buffer

Rename

Buffers (14)

GPR

Completion Bus

Operand Bus

CRF Bus

Two instruction issue to GIQ per clock

One instruction issue to BIQ per clock

L1 Store

Queue Queue

Core Complex Bus

Each execution unit can accept one

instruction per cycle.

e500v2 (9 entry)

e500v2 (5 entry)

e500v1 (4 entry)

e500v1 (3 entry)

Loading...

Loading...