PowerPC e500 Core Family Reference Manual, Rev. 1

12-30 Freescale Semiconductor

Memory Management Units

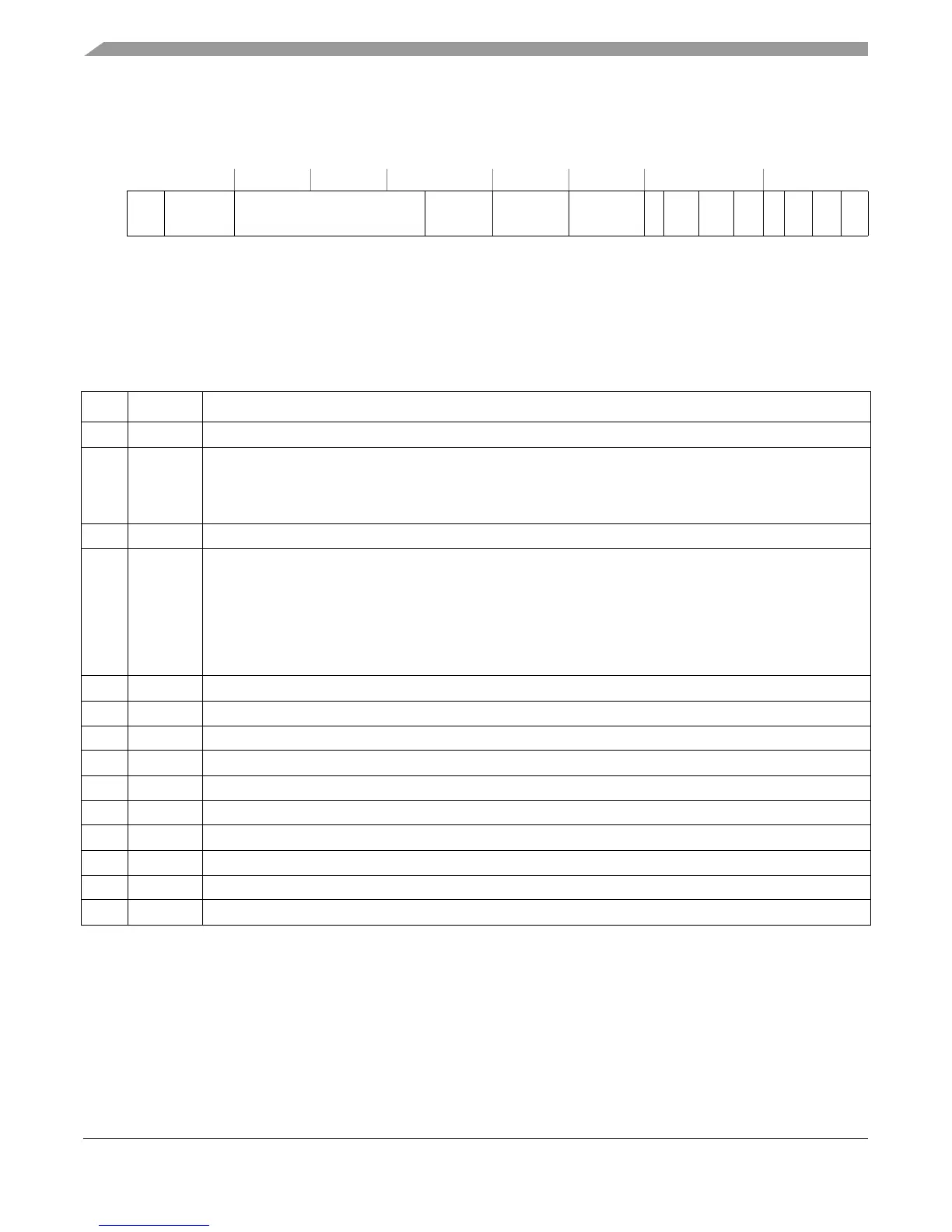

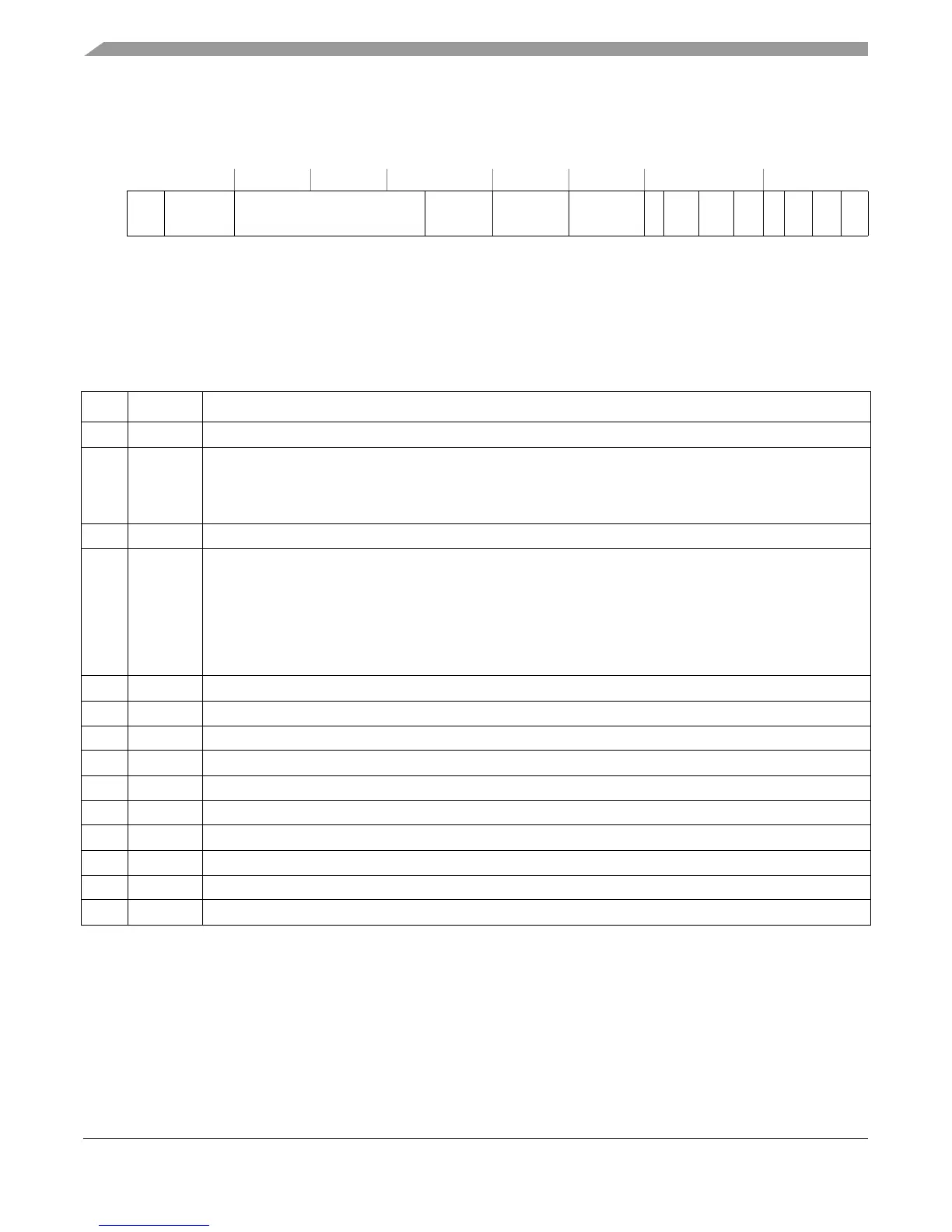

Figure 12-15 describes the format of MAS4 on the e500 core complex.

Table 12-12 shows the core complex MAS4 bit definitions.

Note that MAS5 is not implemented in the e500 core complex.

SPR 628 Access: Supervisor-only

32 33 34 35 36 45 46 47 48 55 56 57 58 59 60 61 62 63

R

— TLBSELD — TIDSELD — TSIZED — X0D X1D WD ID MD GD ED

W

Reset All zeros

Figure 12-15. MAS Register 4 (MAS4)

Table 12-12. MAS4 Field Descriptions—Hardware Replacement Assist

Configuration

Bits Name Description

32–34 — Reserved, should be cleared.

35 TLBSELD TLBSEL default value. The default value to be loaded in MAS0[TLBSEL] on a TLB miss exception. See the

EREF for more information.

0TLB0

1TLB1

36–45 — Reserved, should be cleared.

46–47 TIDSELD TID default selection value. A 2-bit field that specifies which of the current PID registers should be used to

load the MAS1[TID] field on a TLB miss exception.

The e500 implementation defines this field as follows:

00 PID0

01 PID1

10 PID2

11 TIDZ (0x00) (all zeros)

48–51 — Reserved, should be cleared.

52–55 TSIZED Default TSIZE value. Specifies the default value to be loaded into MAS1[TSIZE] on a TLB miss exception.

56 — Reserved, should be cleared.

57 X0D Default X0 value. Specifies the default value to be loaded into MAS2[X0] on a TLB miss exception.

58 X1D Default X1 value. Specifies the default value to be loaded into MAS2[X1] on a TLB miss exception.

59 WD Default W value. Specifies the default value to be loaded into MAS2[W] on a TLB miss exception.

60 ID Default I value. Specifies the default value to be loaded into MAS2[I] on a TLB miss exception.

61 MD Default M value. Specifies the default value to be loaded into MAS2[M] on a TLB miss exception.

62 GD Default G value. Specifies the default value to be loaded into MAS2[G] on a TLB miss exception.

63 ED Default E value. Specifies the default value to be loaded into MAS2[E] on a TLB miss exception.

Loading...

Loading...