PowerPC e500 Core Family Reference Manual, Rev. 1

E-2 Freescale Semiconductor

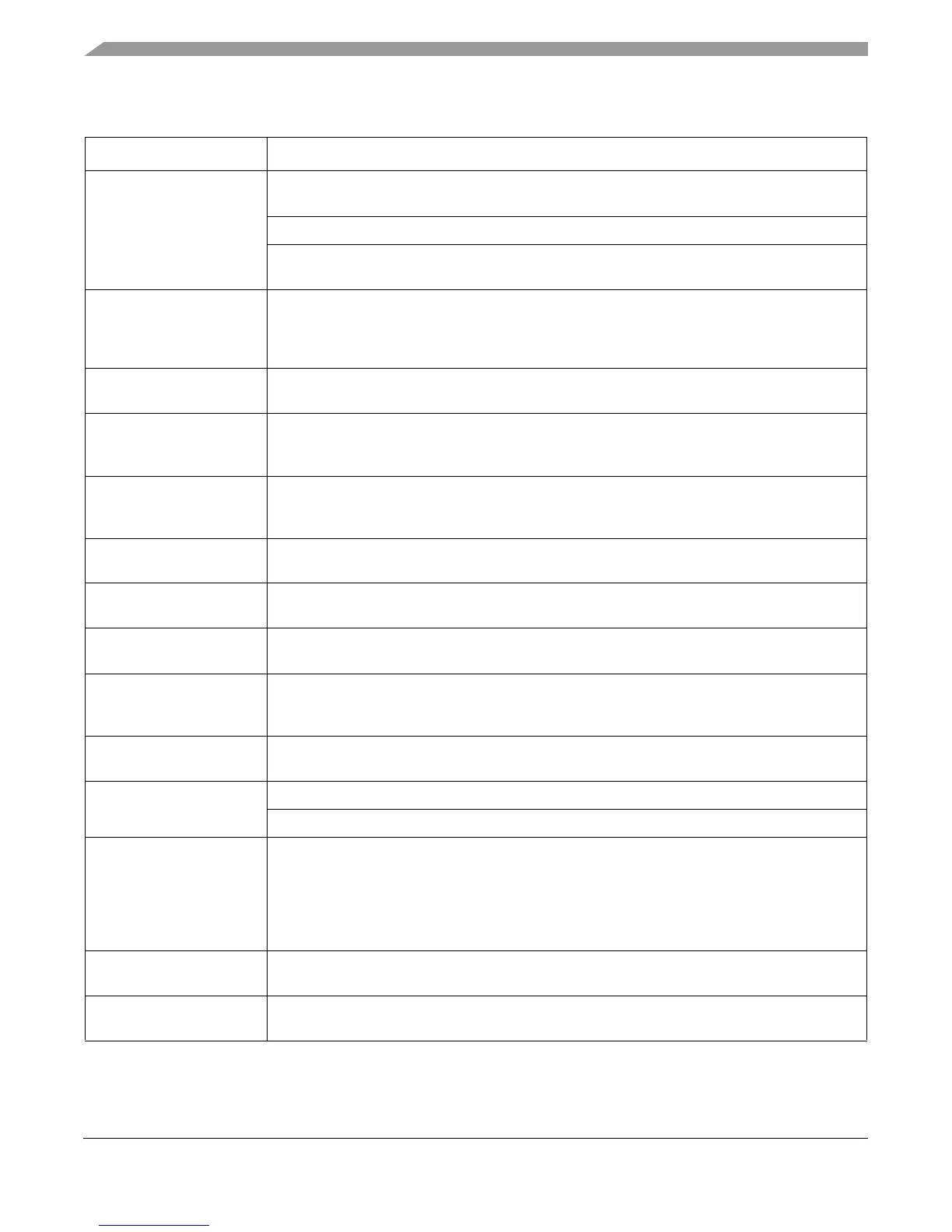

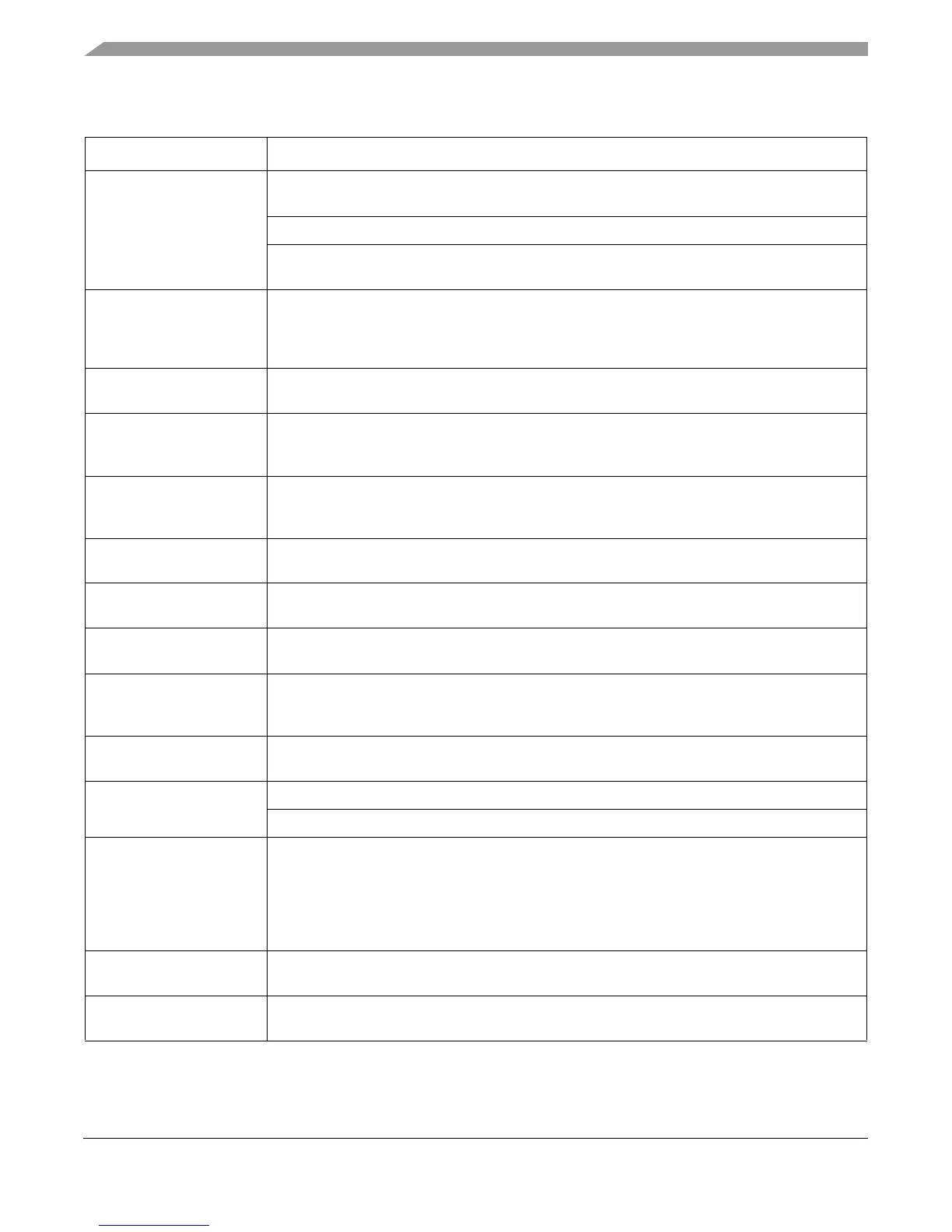

Revision History

Chapter 3, “Instruction

Model”

Scalar and vector embedded floating-point instructions are now considered to be in separate

APUs from the SPE APU.

Added material on double-precision floating-point APU

Notes have been added discouraging use of SPE and embedded floating-point instructions in

PowerQUICC III applications.

Section 3.2.3.1,

“Synchronization

Requirements for

e500-Specific SPRs”

In Ta ble 3- 4 , all of the mtspr to debug register (IAC, DAC, DBCR0, DBCR1, DBSR) instructions

must be followed by a context-synchronizing instruction, but no synchronization is required before

them. Previously, no post-synchronization was shown.

Section 3.3.1.6.1, “mbar

(MO = 1)”

Added section to provide an EIS architectural definition for mbar (MO = 1), which is the classic

PowerPC architecture definition of eieio.

Section 3.3.1.8.1,

“User-Level Cache

Instructions”

In Ta ble 3- 2 6 , the dcbz instruction does not take an alignment interrupt if the cache is disabled.

Section 3.5, “Using msync

and mbar to Order Memory

Accesses”

Added section

Section 3.10, “Instruction

Listing”

Book E 64-bit instructions were removed from Ta bl e 3 -4 4 .

Section 5.3, “Interrupt

Registers

Deleted MCSR[GL_CI] from Ta bl e 5 - 4 . Also removed column “Recoverable” in same table

Section 5.7, “Interrupt

Definitions”

Deleted references to ESR[AP], which is not implemented on the e500.

Chapter 9, “Timer Facilities” Corrected concatenation order of WPEXT || WP and (FPEXT || FP)

TCR[WPEXT] and TCR[FPEXT], not specified in Book E, are concatenated with TCR[WP] and

TCR[FP]

Chapter 10, “Auxiliary

Processing Units (APUs)”

Removed coverage of Freescale Book E–defined APUs. See the EREF for more information.

Chapter 11, “L1 Caches” Removed references to MEI.

Deleted the ‘D’ from the acronyms for the L1CSR0 bit fields

Section 11.2.2, “L1

Instruction Cache

Organization”

Added note: On the e500v1, it is possible for multiple entries in the L1 instruction cache to contain

data for the same physical memory location. This error can occur when two different effective

addresses (EA) map to the same physical address and accesses to these two EAs occur within

the same context and relatively close together in time.

This is avoided by not fetching instructions from one physical address through two or more

different EAs within any given context.

Section 11.2.3, “L1 Cache

Parity”

Added section. .

Section 11.2.4, “Cache

Parity Error Injection”

Changed name of L1CSR0[PEIE] to CPI and L1CSR1[IPEIE] to ICPI. Added requirement to have

cache parity checking enabled if cache parity injection is enabled.

Table E-1. Revision History

Chapter or Section Description

Loading...

Loading...