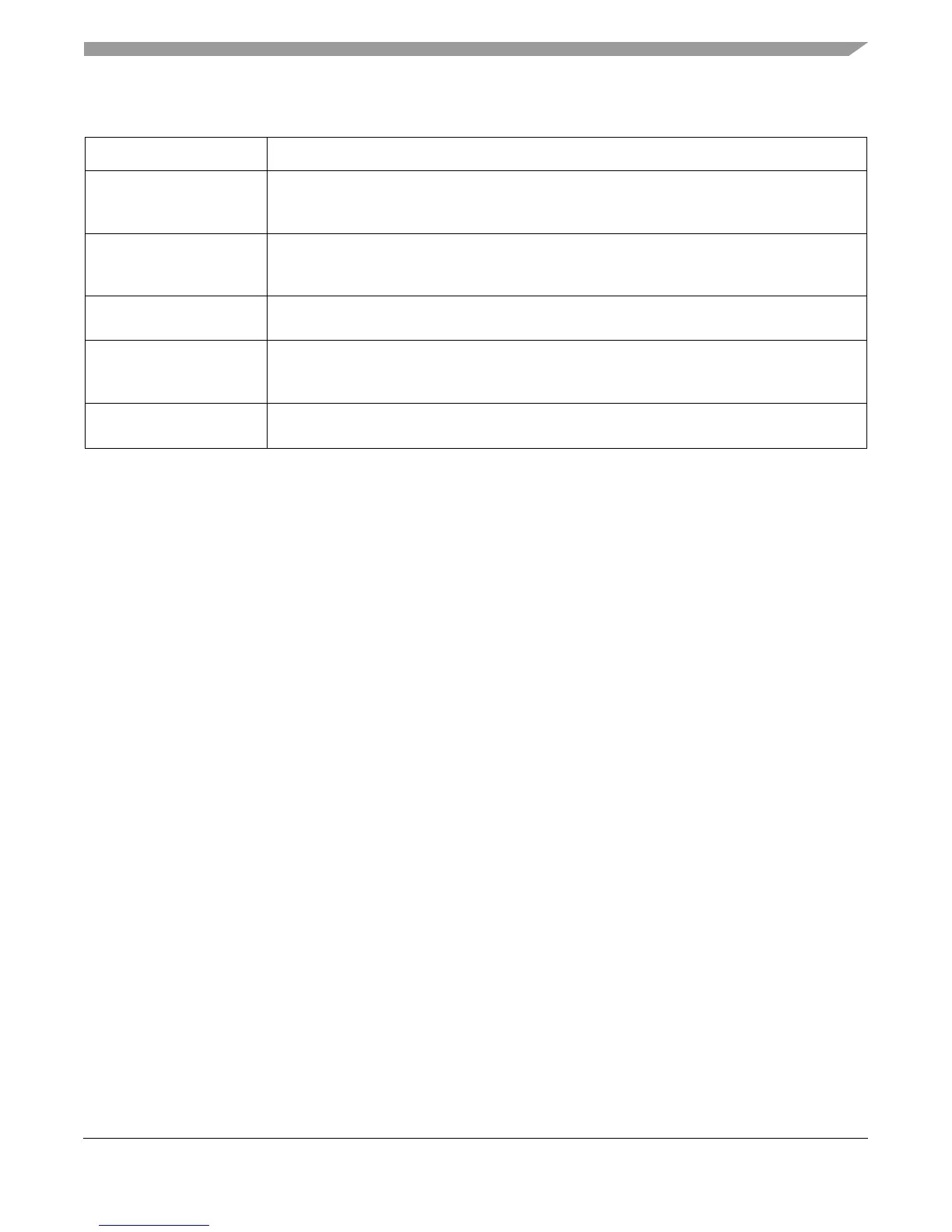

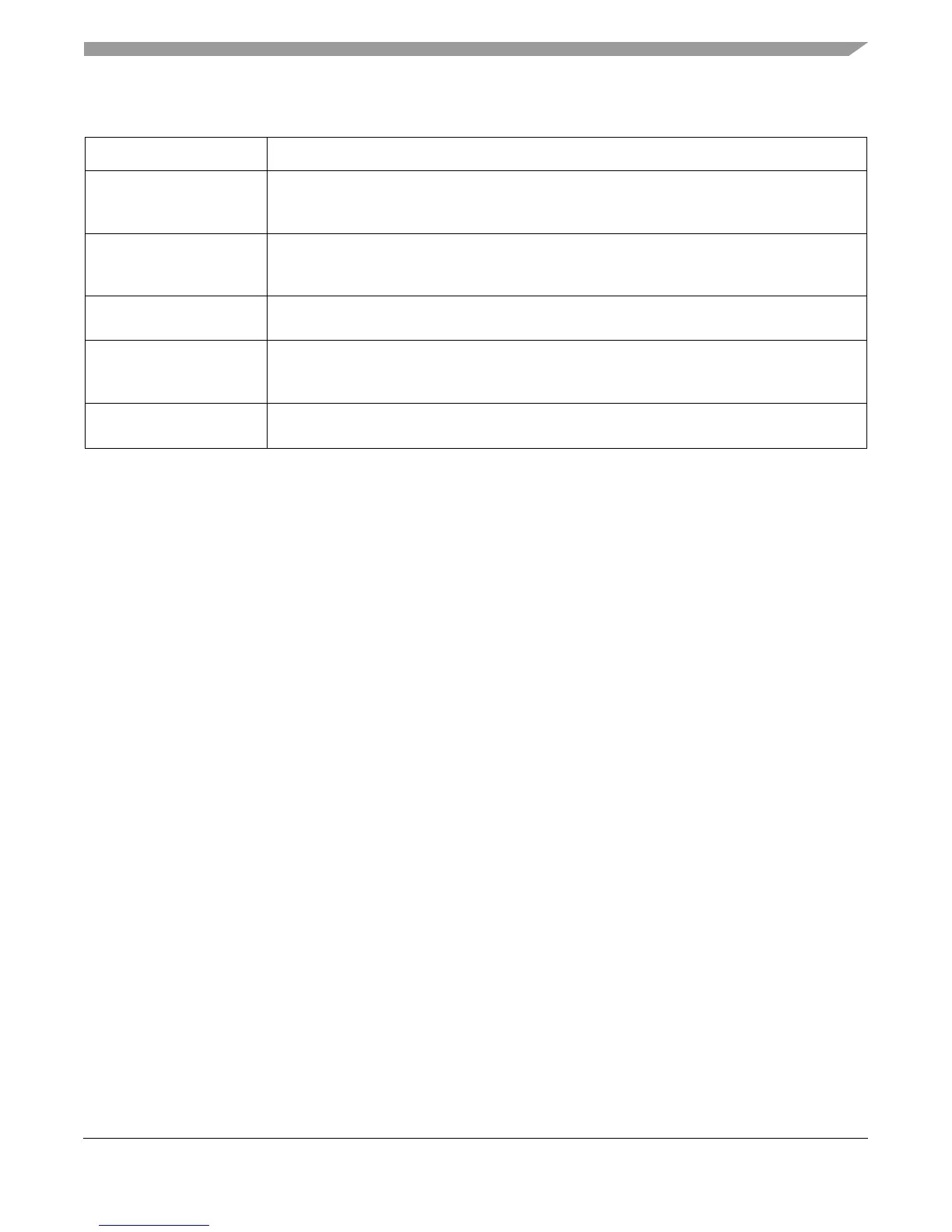

Revision History

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor E-3

Section 11.3.4.5,

“Speculative Accesses to

Guarded Memory”

Added caution about cacheable and guarded loads for e500v1

Section 11.3.5.2,

“Sequential Consistency of

Memory Accesses”

Replaced “Newer caching-allowed loads can bypass older caching-allowed loads only if the two

loads are to different 32-byte address granules” with “Newer non-guarded, caching-allowed loads

can bypass older non-guarded, caching-allowed loads.”

Chapter 12, “Memory

Management Units”

Removed references to SHAREN, SHAREND, MEI

Section 12.2,

“Effective-to-Real Address

Translation”

Corrected bit number compositions in effective-to-real address translation figures, Figure 12-1

and Figure 12-2

Chapter 13, “Core Complex

Bus (CCB)”

Added chapter

Table E-1. Revision History

Chapter or Section Description

Loading...

Loading...