Instruction Model

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 3-63

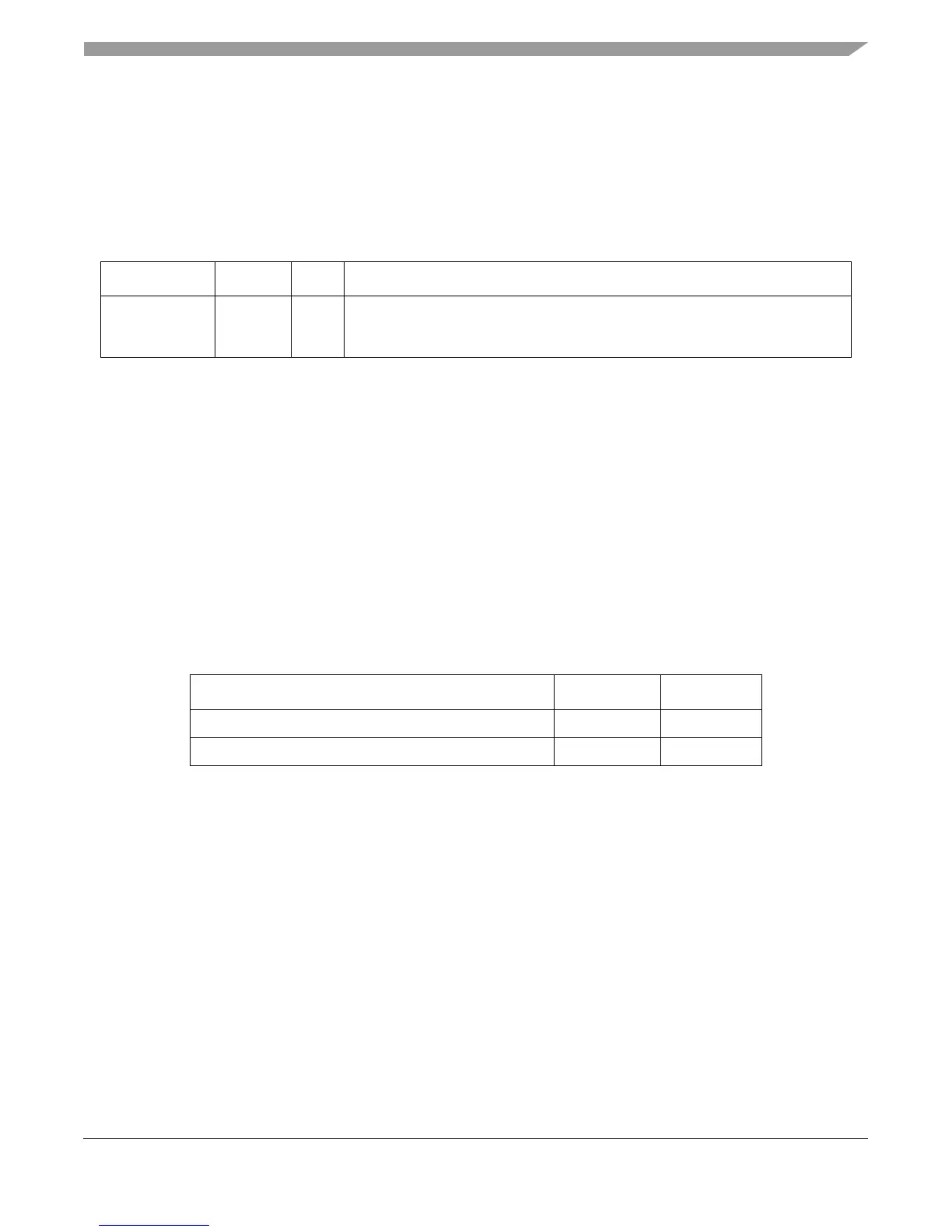

3.8.5 Machine Check APU

The machine check APU defines a separate interrupt type for machine check interrupts. It provides

additional save and restore SPRs (MCSRR and MCSRR1). The Return from Machine Check

Interrupt instruction (rfmci), is described in Table 3-42.

3.9 e500-Specific Instructions

The e500 implements the branch target buffer locking APU, which is not part of the EIS. It defines

the two instructions described in the following section.

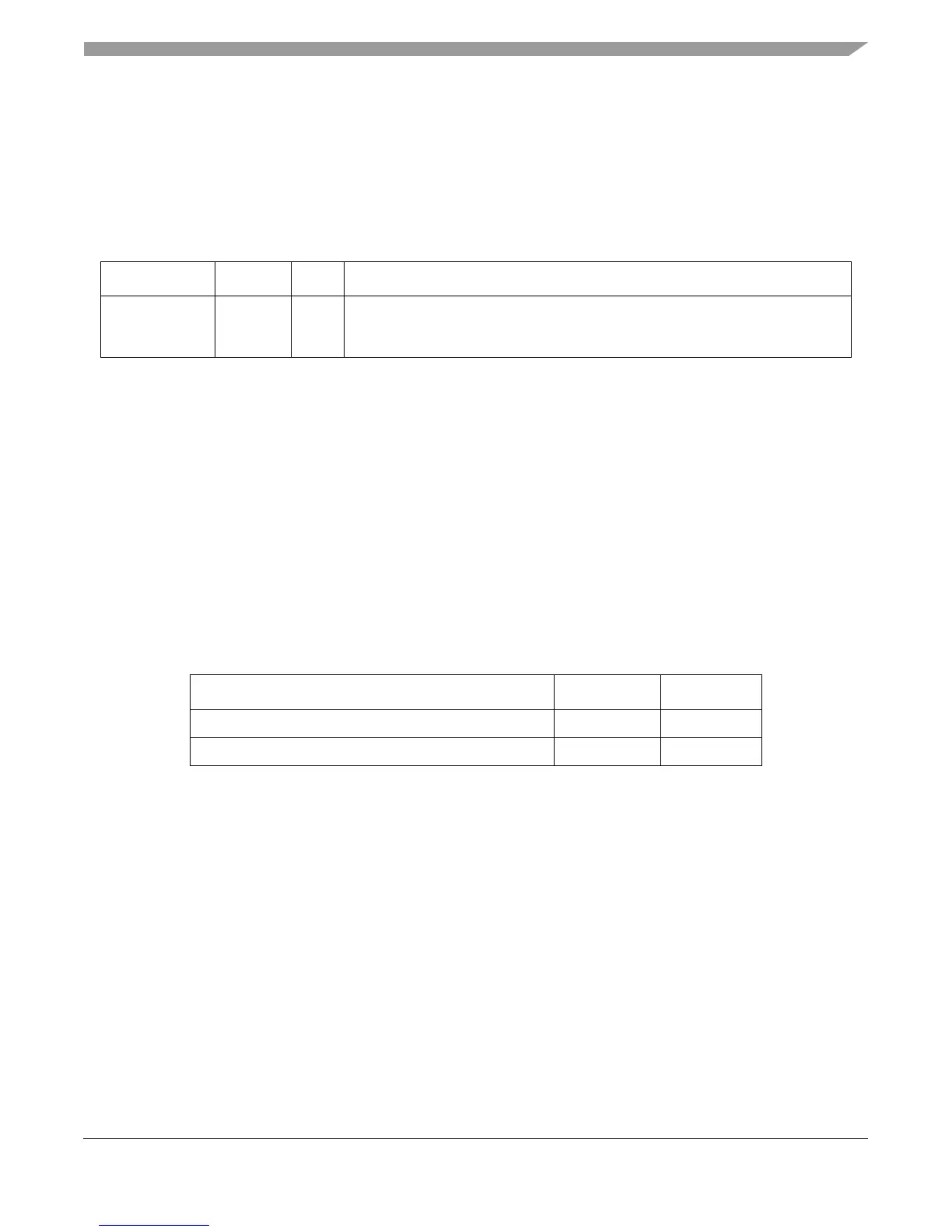

3.9.1 Branch Target Buffer (BTB) Locking Instructions

The e500 core complex provides a 512-entry BTB for efficient processing of branch instructions.

The BTB is a branch target address cache (BTAC), organized as 128 rows with four-way set

associativity, that holds the address of the target instruction of the 512 most-recently taken

branches. Table 3-43 lists the BTB instructions.

The branch buffer entry address register (BBEAR) and the branch buffer target address register

(BBTAR) are defined in the e500 core complex for enabling the locking and unlocking of BTB

entries. They can be read and written in both user and supervisor modes with mfspr and mtspr.

The user branch locking enable bit, MSR[UBLE], is defined to allow user mode programs to lock

or unlock entries in the BTB. See Chapter 4, “Execution Timing.”

Table 3-42. Machine Check APU Instruction

Name Mnemonic Syntax Implementation Notes

Return from

Machine Check

Interrupt

rfmci — When rfmci is executed, the values in MCSRR0 and MCSRR1 are restored. rfmci

is context-synchronizing; it works its way to the final execute stage, updates

architected registers, and redirects instruction flow.

Table 3-43. Branch Target Buffer (BTB) Instructions

Name Mnemonic Syntax

Branch Buffer Entry Lock Reset bbelr —

Branch Buffer Load Entry and Lock Set bblels —

Loading...

Loading...