PowerPC e500 Core Family Reference Manual, Rev. 1

7-4 Freescale Semiconductor

Performance Monitor

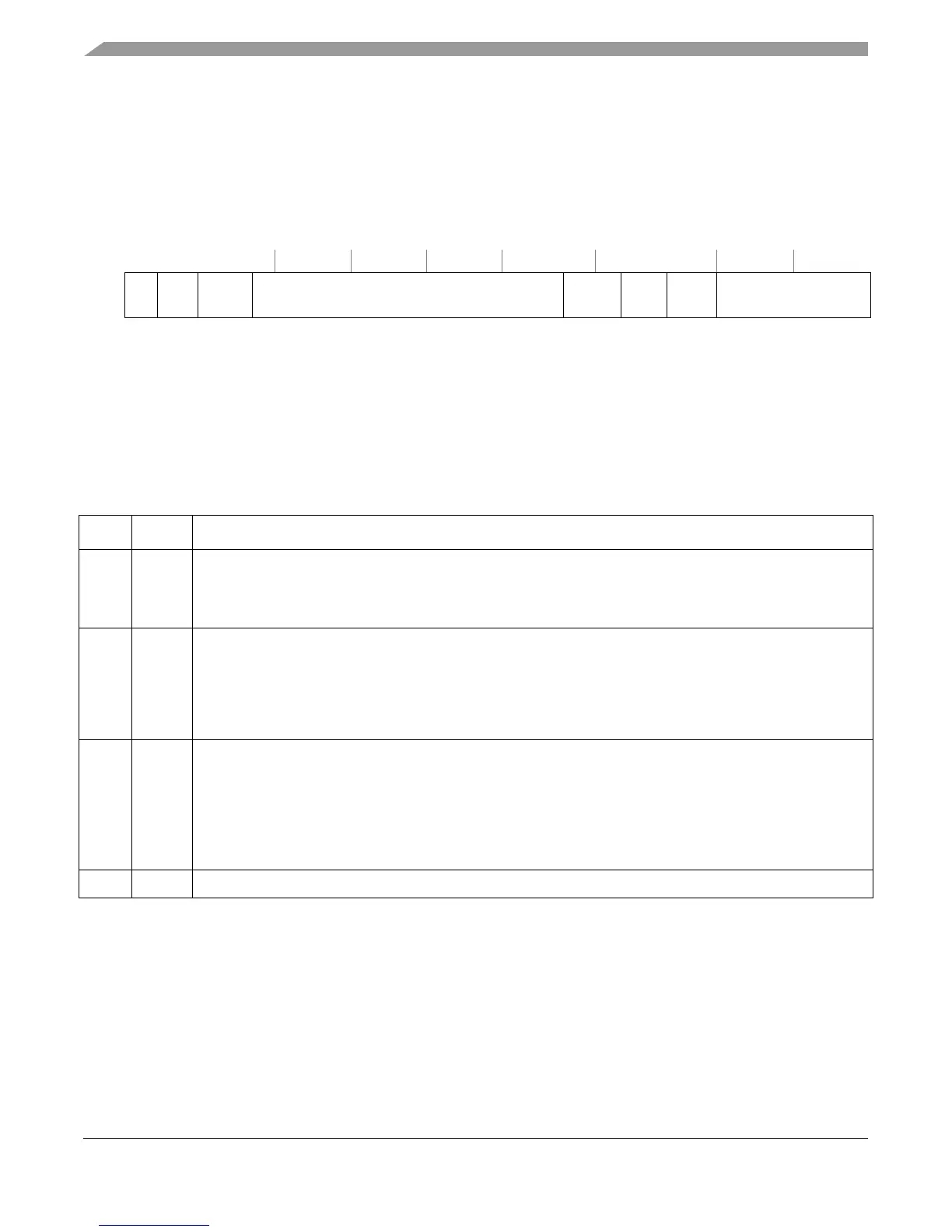

7.2.1 Global Control Register 0 (PMGC0)

The performance monitor global control register (PMGC0), shown in Figure 7-1, controls all

performance monitor counters.

PMGC0 is cleared by a hard reset. Reading this register does not change its contents. Table 7-3

describes PMGC0 fields.

PMGC0 (PMR400)

UPMGC0 (PMR384)

Access: PMGC0: Supervisor-only

UPMGC0: Supervisor/user read-only

32 33 34 35 50 51 52 53 54 55 56 63

R

FAC PMIE FCECE — TBSEL

1

— TBEE

1

—

W

Reset All zeros

1

e500v2 only

Figure 7-1. Performance Monitor Global Control Register 0 (PMGC0)/

User Performance Monitor Global Control Register 0 (UPMGC0)

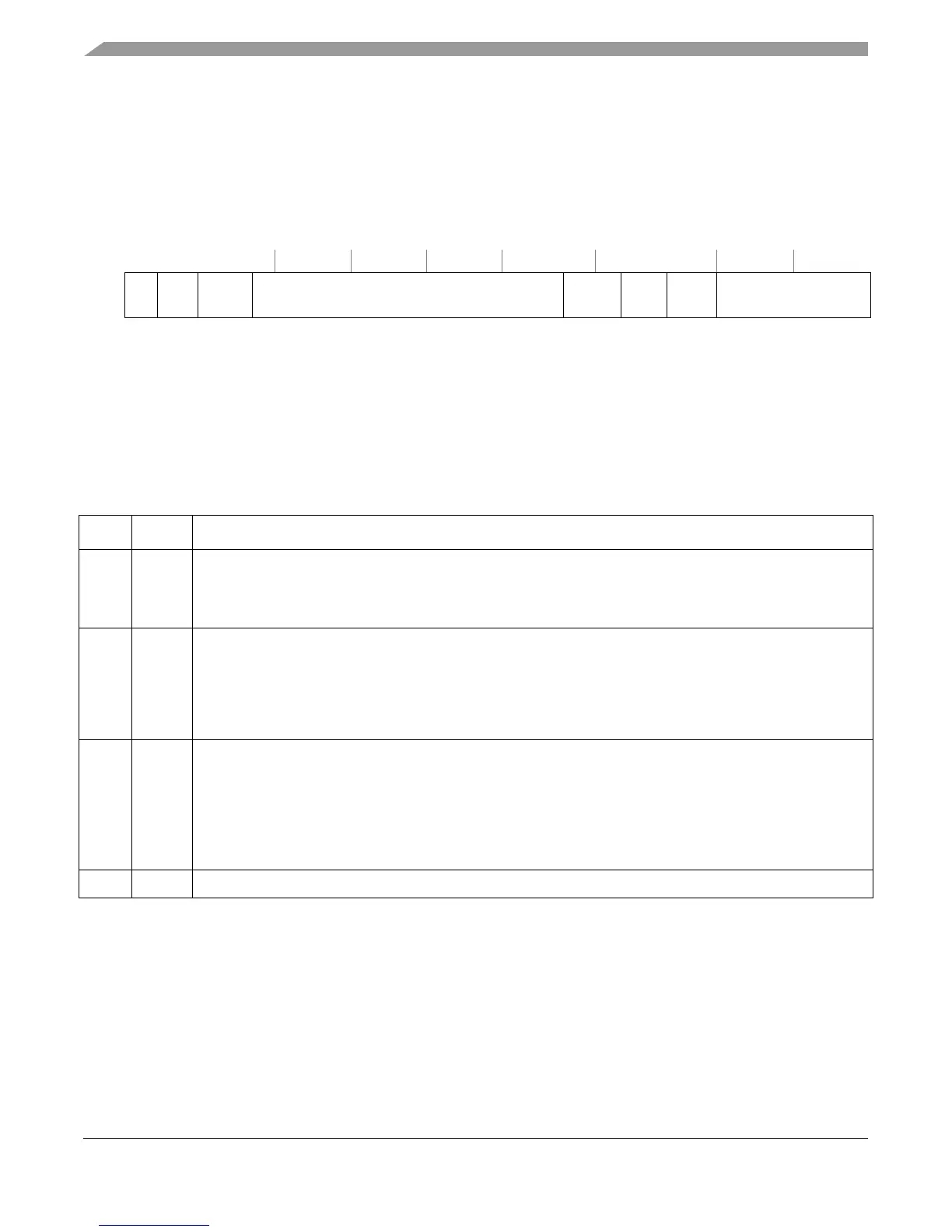

Table 7-3. PMGC0 Field Descriptions

Bits Name Description

32 FAC Freeze all counters. When FAC is set by hardware or software, PMLCx[FC] maintains its current value until it

is changed by software.

0 The PMCs are incremented (if permitted by other PM control bits).

1 The PMCs are not incremented.

33 PMIE Performance monitor interrupt enable

0 Performance monitor interrupts are disabled.

1 Performance monitor interrupts are enabled and occur when an enabled condition or event occurs, at which

time PMGC0[PMIE] is cleared

Software can clear PMIE to prevent performance monitor interrupts. Performance monitor interrupts are

caused by time base events or PMCx overflow.

34 FCECE Freeze counters on enabled condition or event

0 The PMCs can be incremented (if permitted by other PM control bits).

1 The PMCs can be incremented (if permitted by other PM control bits) only until an enabled condition or event

occurs. When an enabled condition or event occurs, PMGC0[FAC] is set. It is up to software to clear FAC.

An enabled condition or event is defined as one of the following:

• When the msb = 1 in PMC

x

and PMLCa

x

[CE] = 1.

• When the time-base bit specified by TBSEL=1 and TBEE=1.

35–50 — Reserved, should be cleared.

Loading...

Loading...