PowerPC e500 Core Family Reference Manual, Rev. 1

2-10 Freescale Semiconductor

Register Model

2.4.2 Link Register (LR)

The e500 implements the LR as it is defined by Book E.

The link register can be used to provide the branch target address for a Branch Conditional to LR

instruction, and it holds the return address after branch and link instructions.

2.4.3 Count Register (CTR)

The e500 implements the CTR as it is defined by Book E. The CTR can be used to hold a loop

count that can be decremented and tested during execution of branch instructions that contain an

appropriately encoded BO field. If the CTR value is 0 before being decremented, it is –1 afterward.

The entire CTR can be used to hold the branch target address for a Branch Conditional to CTR

(bcctrx) instruction.

2.5 Processor Control Registers

This section addresses machine state, processor ID, and processor version registers.

2.5.1 Machine State Register (MSR)

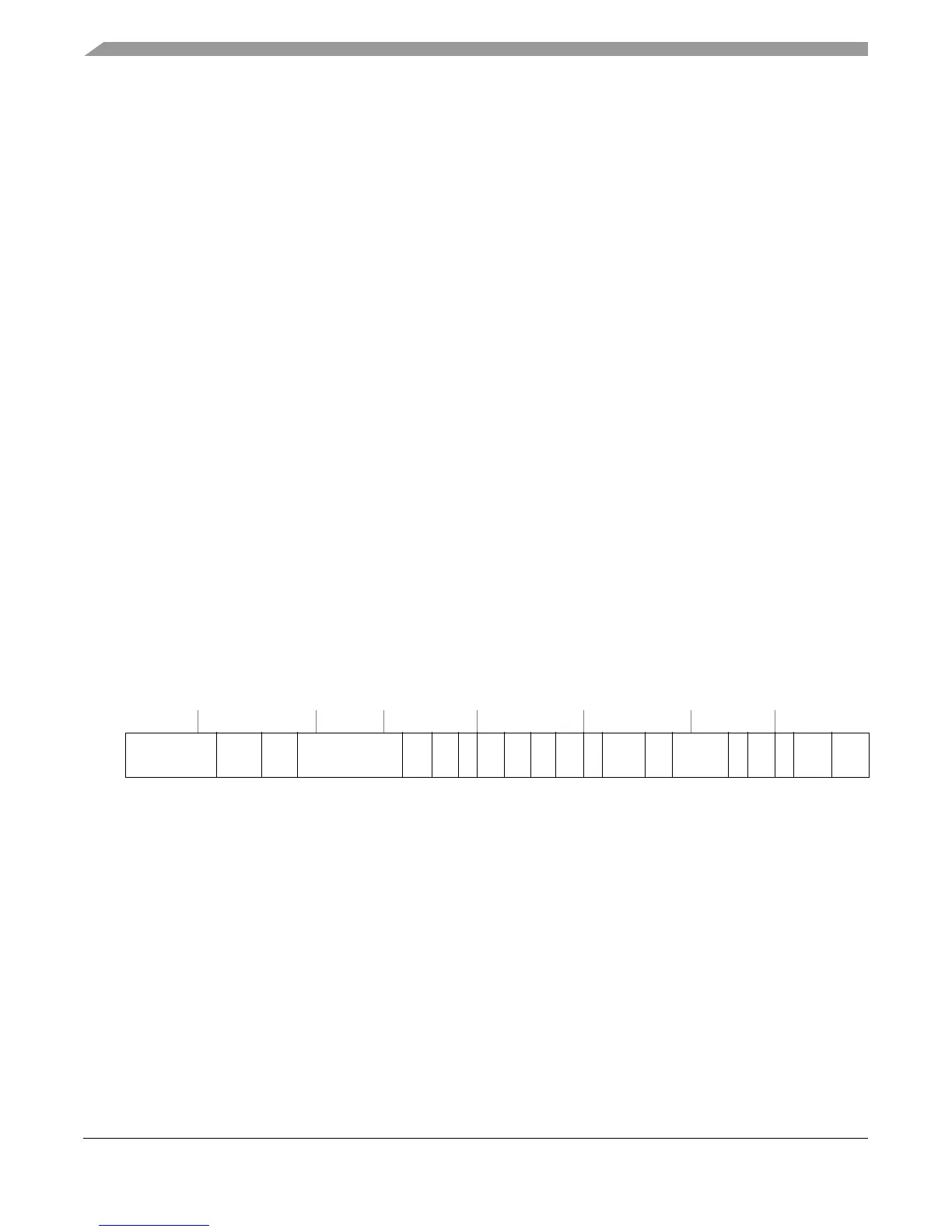

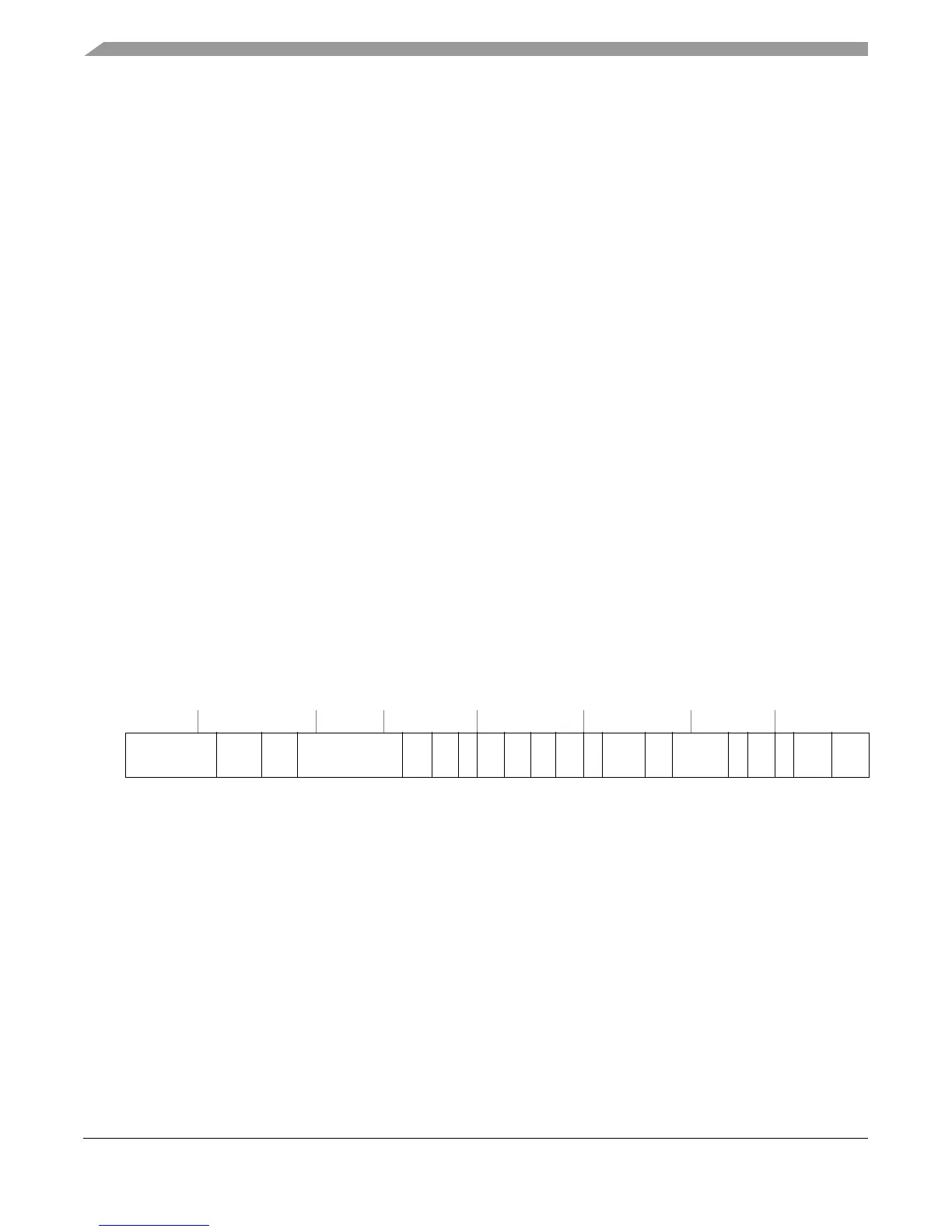

The machine state register (MSR), shown in Figure 2-2, defines the state of the processor (that is,

enabling and disabling of interrupts and debugging exceptions, enabling and disabling of address

translation for instruction and data memory accesses, enabling and disabling some APUs, and

specifying whether the processor is in supervisor or user mode).

MSR contents are automatically saved, altered, and restored by the interrupt-handling mechanism.

If a non-critical interrupt is taken, MSR contents are automatically copied into SRR1. If a critical

interrupt is taken, MSR contents are automatically copied into CSRR1. When an rfi or rfci is

executed, MSR contents are restored from SRR1 or CSRR1. The e500 implements the machine

check interrupt differently than it is defined in Book E. When a machine check interrupt is taken,

MCSRR0 and MCSRR1 hold the return address and MSR information. The EIS defines the Return

from Machine Check Interrupt instruction, rfmci, which restores MSR contents from MCSRR1

when it is executed.

Access: Supervisor-only

32 36 37 38 39 44 45 46 47 48 49 50 51 52 53 54 55 57 58 59 60 61 62 63

R

— UCLE SPE — WE CE — EE PR FP ME —UBLE DE — IS DS —PMM —

W

Reset All zeros

Figure 2-2. Machine State Register (MSR)

Loading...

Loading...