Core Complex Overview

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 1-27

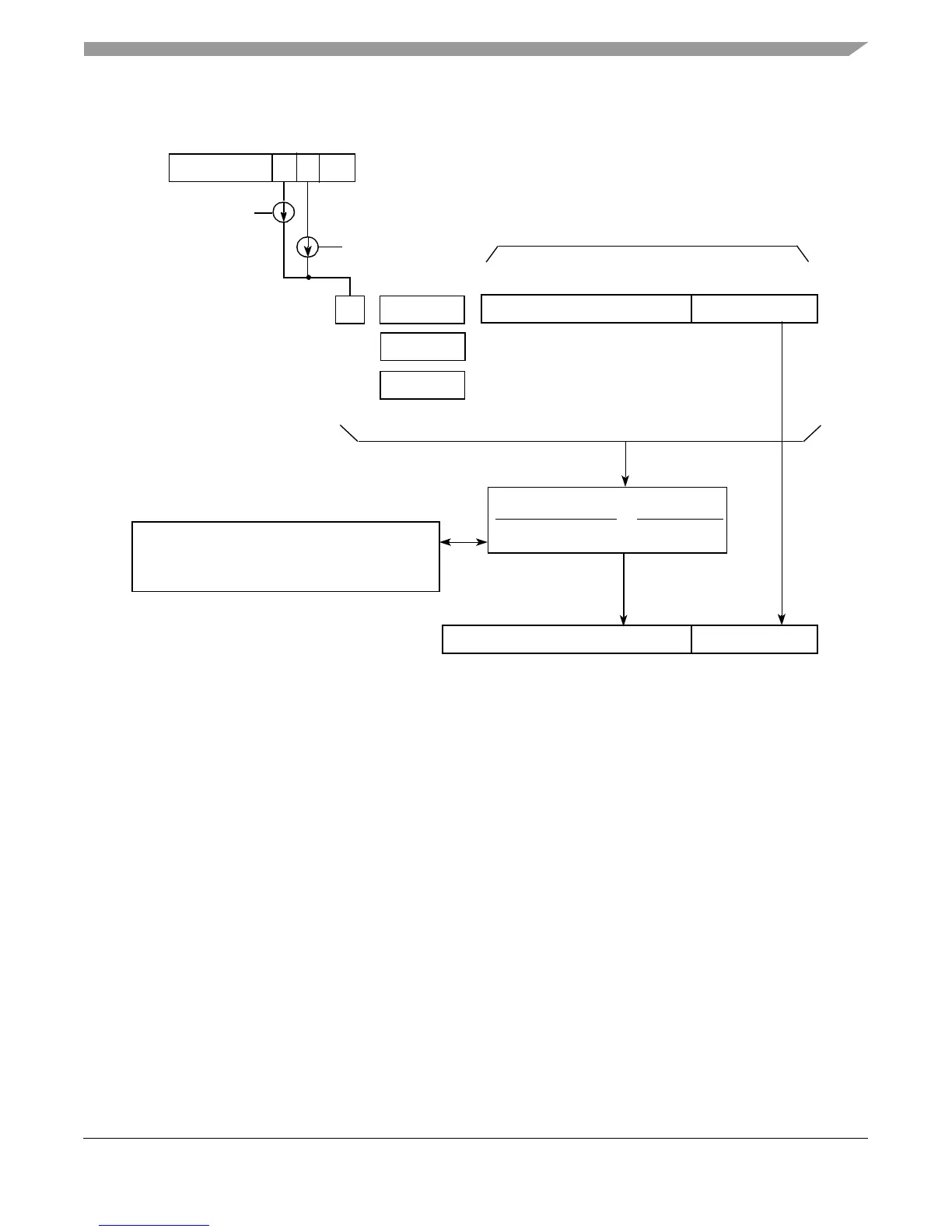

Figure 1-10 shows the same translation flow for the e500v2 core.

Figure 1-10. Effective-to-Real Address Translation Flow (e500v2)

The appropriate L1 MMU (instruction or data) is checked for a matching address translation. The

instruction L1 MMU and data L1 MMU operate independently and can be accessed in parallel, so

that hits for instruction accesses and data accesses can occur in the same clock. If an L1 MMU

misses, the request for translation is forwarded to the unified (instruction and data) L2 MMU. If

found, the contents of the TLB entry are concatenated with the byte address to obtain the physical

address of the requested access. On misses, the L1 TLB entries are replaced from their L2 TLB

counterparts using a true LRU algorithm.

1.9.2 MMU Assist Registers (MAS0–MAS4 and MAS6–MAS7)

Book E defines SPR numbers for the MMU assist registers, which are used to hold values either

read from or to be written to the TLBs and information required to identify the TLB to be accessed.

To ensure consistency among Freescale Semiconductor Book E processors, certain aspects of the

implementation are defined by the Freescale Semiconductor Book E standard, whereas more

specific details are left to individual implementations. MAS3 implements the real page number

Effective Page Number Byte Address

Real Page Number Byte Address

32-bit Effective Address (EA)

36-bit Real Address

0–20 bits*

4–24 bits* 12–32 bits*

L2 MMU (unified)

Three 41-bit Virtual Addresses (VAs)

8 bits

MSR

••• IS DS •••

Instruction Access

Data Access

AS

PID0

PID1

PID2

L1 MMUs

Instruction L1 MMU

Data L1 MMU

2 TLBs 2 TLBs

* Number of bits depends on page size

(4 Kbytes–4 Gbytes)

16-Entry Fully-Assoc. VSP Array (TLB1)

512-Entry 4-Way Set Assoc. Array (TLB0)

12–32 bits*

Loading...

Loading...