PowerPC e500 Core Family Reference Manual, Rev. 1

2-42 Freescale Semiconductor

Register Model

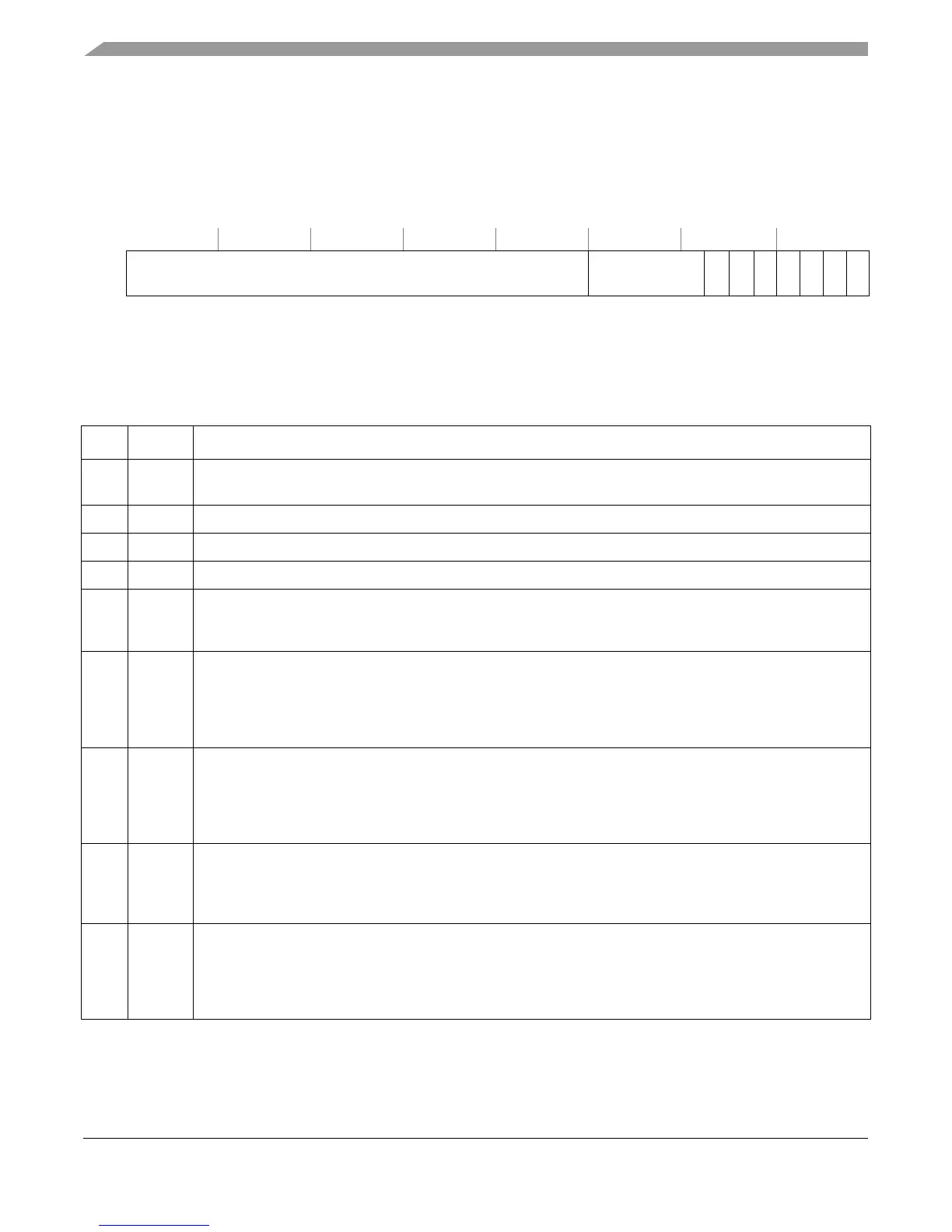

2.12.5.3 MAS Register 2 (MAS2)

Figure 2-31 shows the format of MAS2. Writing to MAS2 requires synchronization, as described

in Section 2.16, “Synchronization Requirements for SPRs.”

The MAS2 fields are described in Table 2-26.

SPR 626 Access: Supervisor-only

32 51 52 56 57 58 59 60 61 62 63

R

EPN —X0X1WIMGE

W

Reset All zeros

Figure 2-31. MAS Register 2 (MAS2)

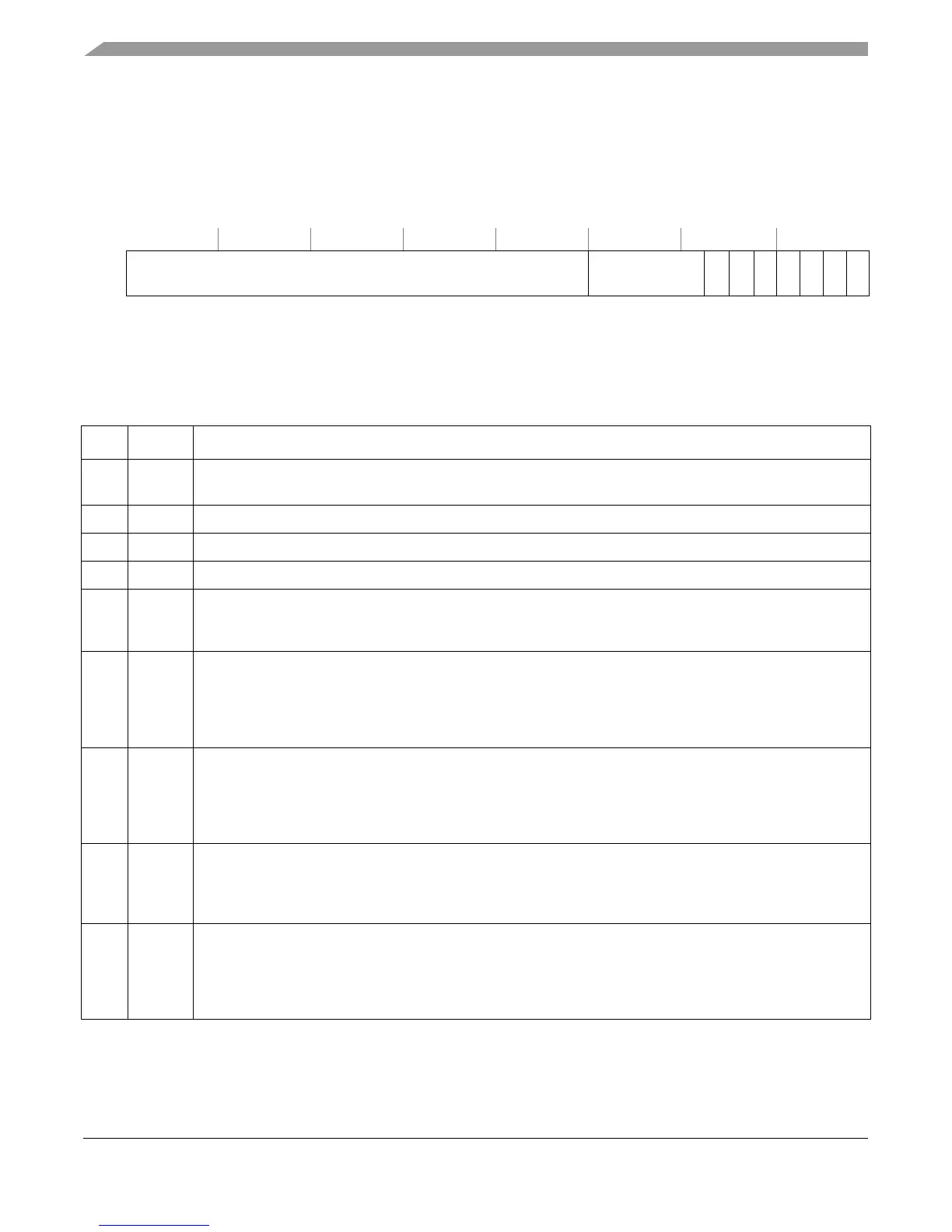

Table 2-26. MAS2 Field Descriptions—EPN and Page Attributes

Bits Name Description

32–51 EPN Effective page number. Depending on page size, only the bits associated with a page boundary are valid. Bits

that represent offsets within a page are ignored and should be zero.

52–56 — Reserved, should be cleared

57 X0 Implementation-dependent page attribute

58 X1 Implementation-dependent page attribute

59 W Write-through

0 This page is considered write-back with respect to the caches in the system.

1 All stores performed to this page are written through the caches to main memory.

60 I Caching-inhibited

0 Accesses to this page are considered cacheable.

1 The page is considered caching-inhibited. All loads and stores to the page bypass the caches and are

performed directly to main memory. A read or write to a caching-inhibited page affects only the memory

element specified by the operation.

61 M Memory coherency required

0 Memory coherency is not required.

1 Memory coherency is required. This allows loads and stores to this page to be coherent with loads and

stores from other processors (and devices) in the system, assuming all such devices are participating in the

coherency protocol.

62 G Guarded

0 Accesses to this page are not guarded and can be performed before it is known if they are required by the

sequential execution model.

1 All loads and stores to this page are performed without speculation (that is, they are known to be required).

63 E Endianness. Determines endianness for the corresponding page. Little-endian operation is true little endian,

which differs from the modified little-endian byte ordering model optionally available in previous devices that

implement the PowerPC architecture.

0 The page is accessed in big-endian byte order.

1 The page is accessed in true little-endian byte order.

Loading...

Loading...