PowerPC e500 Core Family Reference Manual, Rev. 1

2-26 Freescale Semiconductor

Register Model

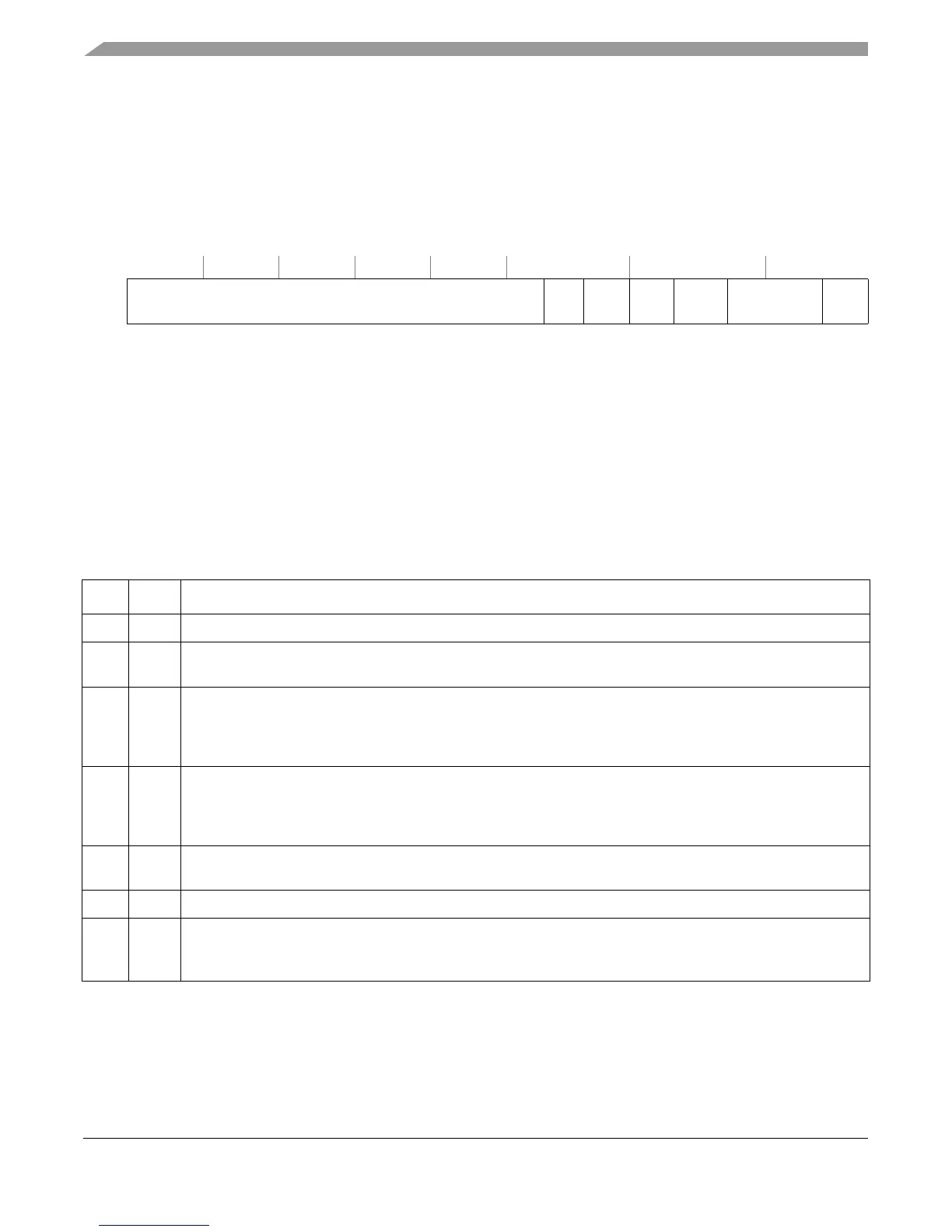

2.9.3 Branch Unit Control and Status Register (BUCSR)

The BUCSR, shown in Figure 2-17, is used for general control and status of the branch target

buffer (BTB). Writing to BUCSR requires synchronization, as described in Section 2.16,

“Synchronization Requirements for SPRs.”

BUCSR provides control of BTB locking, including the following:

• Enable or disable BTB locking

• Invalidate all BTB entries at once (flash invalidate)

• Unlock all BTB entries at once (flash lock clear)

Table 2-13 describes the BUCSR fields.

SPR 1013 Access: Supervisor-only

32 53 54 55 56 57 58 62 63

R

— BBFI BBLO BBUL BBLFC — BPEN

W

Reset All zeros

Figure 2-17. Branch Unit Control and Status Register (BUCSR)

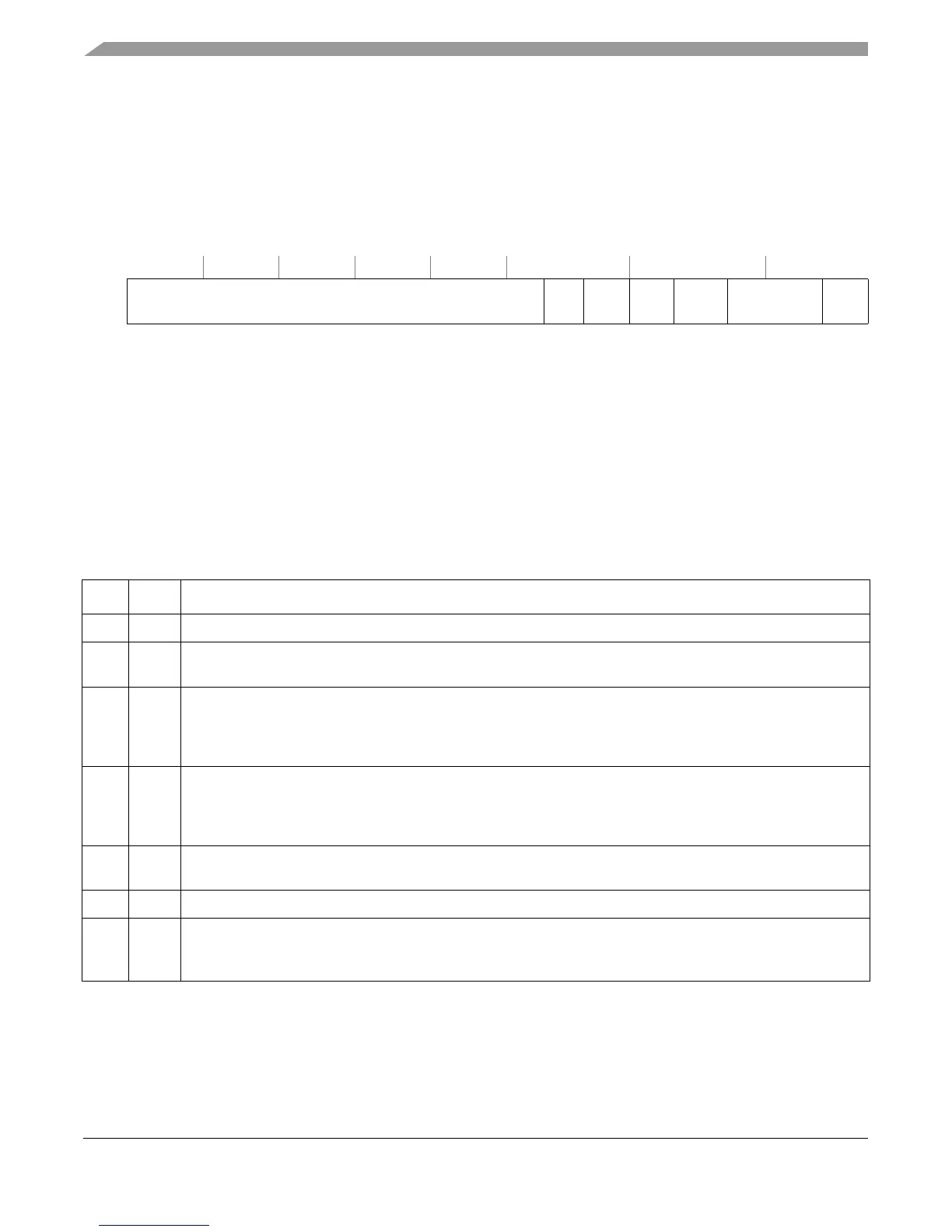

Table 2-13. BUCSR Field Descriptions

Bits Name Description

32–53 — Reserved, should be cleared.

54 BBFI Branch buffer flash invalidate. Clearing and then setting BBFI flash clears the valid bit of all entries in the branch

buffer; clearing occurs independently from the value of the enable bit (BPEN). BBFI is always read as 0.

55 BBLO Branch buffer lock overflow status

0 Indicates a lock overflow condition was not encountered in the branch buffer

1 Indicates a lock overflow condition was encountered in the branch buffer

This sticky bit is set by hardware and is cleared by writing 0 to this bit location.

56 BBUL Branch buffer unable to lock

0 Indicates a lock overflow condition in the branch buffer

1 Indicates a lock set instruction failed in the branch buffer, for example, if the BTB is disabled

This sticky bit is set by hardware and is cleared by writing 0 to this bit location.

57 BBLFC Branch buffer lock bits flash clear. Clearing and then setting BBLFC flash clears the lock bit of all entries in the

branch buffer; clearing occurs independently from the value of the enable bit (BPEN). BBLFC is always read as 0.

58–62 — Reserved, should be cleared.

63 BPEN Branch prediction enable

0 Branch prediction disabled

1 Branch prediction enabled (enables BTB to predict branches)

Loading...

Loading...