Register Model

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 2-29

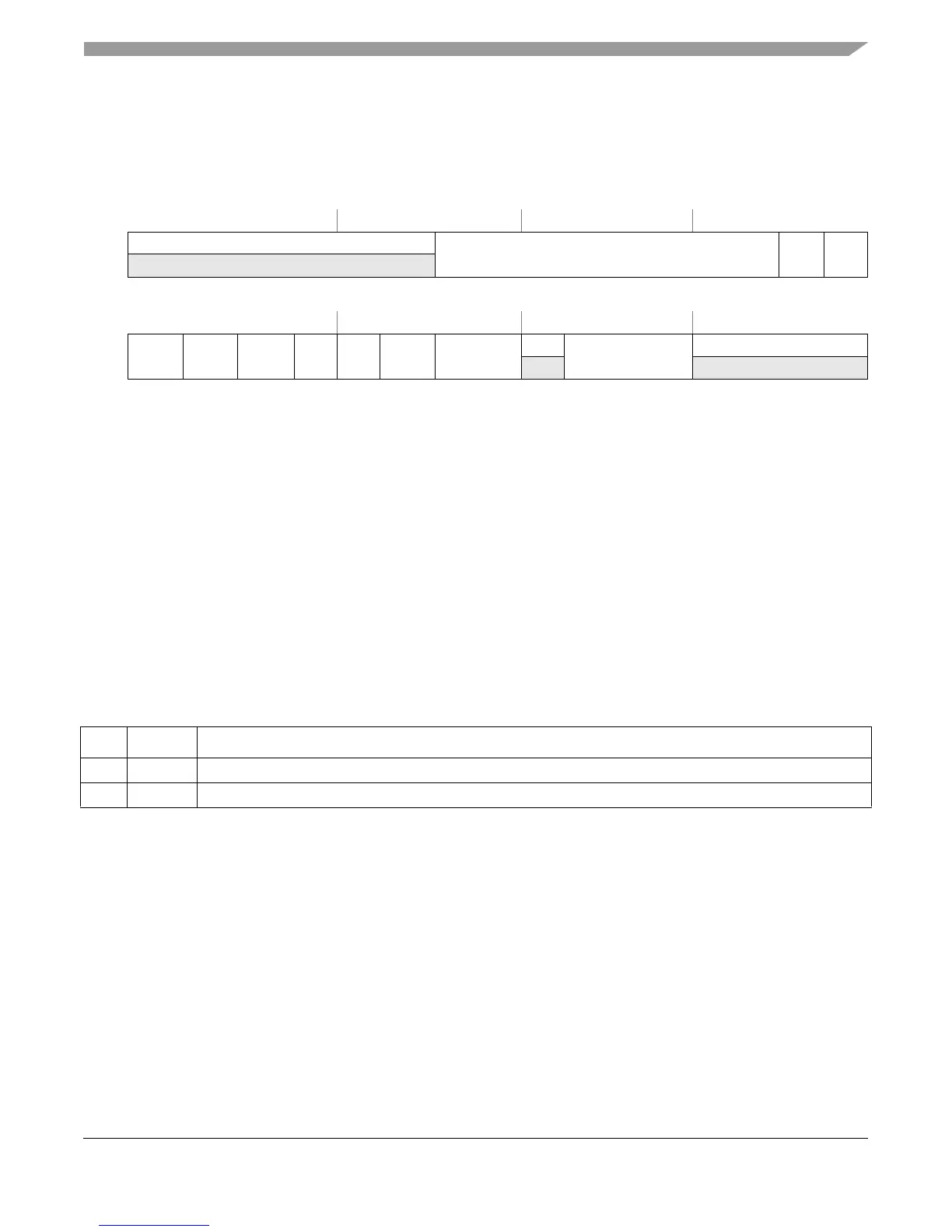

2.10.2 Hardware Implementation-Dependent Register 1 (HID1)

This section describes the HID1 register, shown in Figure 2-19, as it is defined by the e500 core.

NOTE

Note that some HID fields may not be implemented in a device that

incorporates the e500 core and that some fields may be defined more

specifically by the incorporating device. For specific details it is

important to refer to the “Register Summary” chapter in the device’s

reference manual.

HID1 is used for bus configuration and control. Writing to HID1 requires synchronization, as

described in Section 2.16, “Synchronization Requirements for SPRs.”

Table 2-15 describes the HID1 fields.

SPR 1009 Access: Supervisor-only

32 37 38 45 46 47

R PLL_CFG

—

RFXE —

W

Reset All zeros

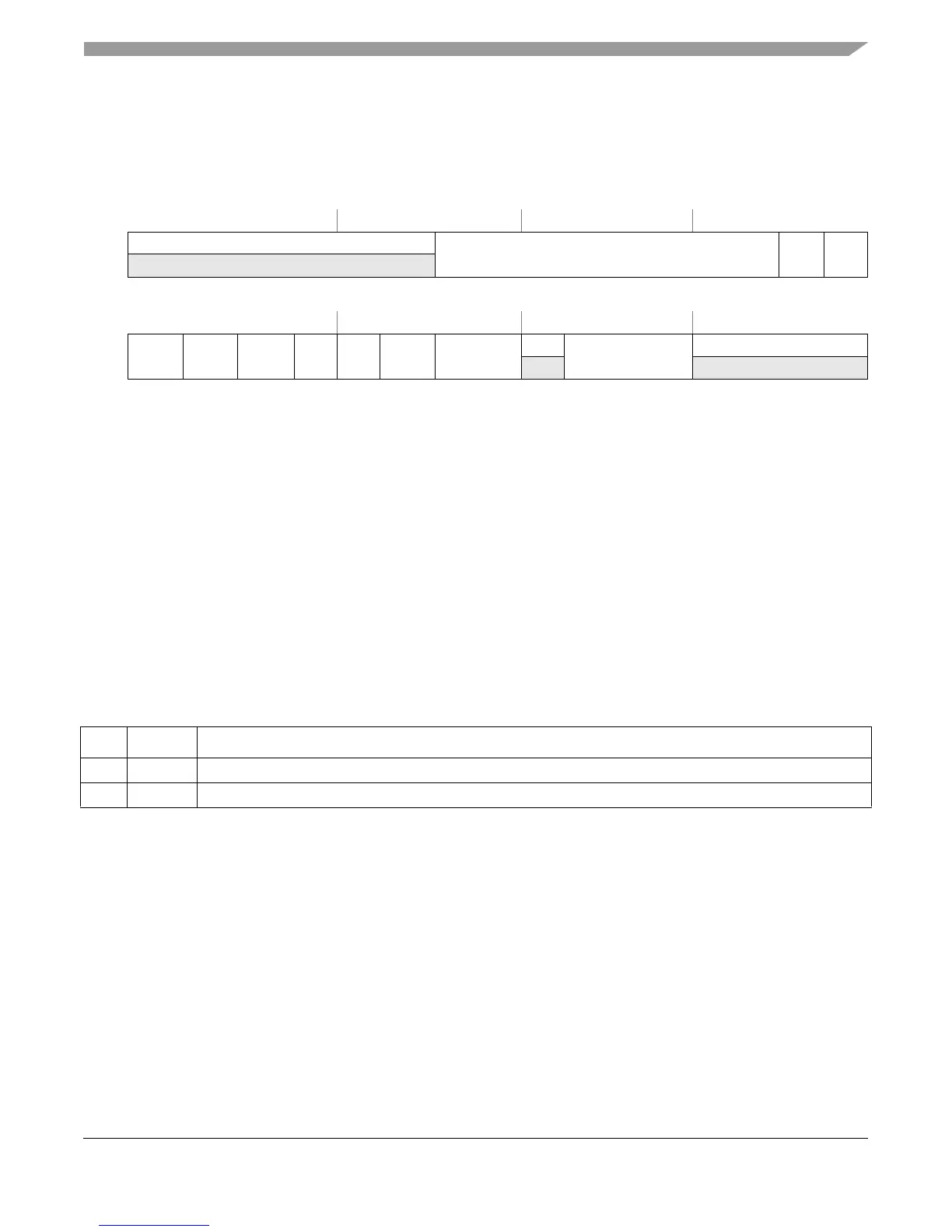

48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63

R

R1DPE R2DPE ASTME ABE — MPXTT —

AT S

—

MID

W

Reset All zeros

Figure 2-19. Hardware Implementation-Dependent Register 1 (HID1)

Table 2-15. HID1 Field Descriptions

Bits Name Description

32–37 PLL_CFG Reflected directly from the PLL_CFG input pins (read-only)

38–46 — Reserved, should be cleared.

Loading...

Loading...