PowerPC e500 Core Family Reference Manual, Rev. 1

2-30 Freescale Semiconductor

Register Model

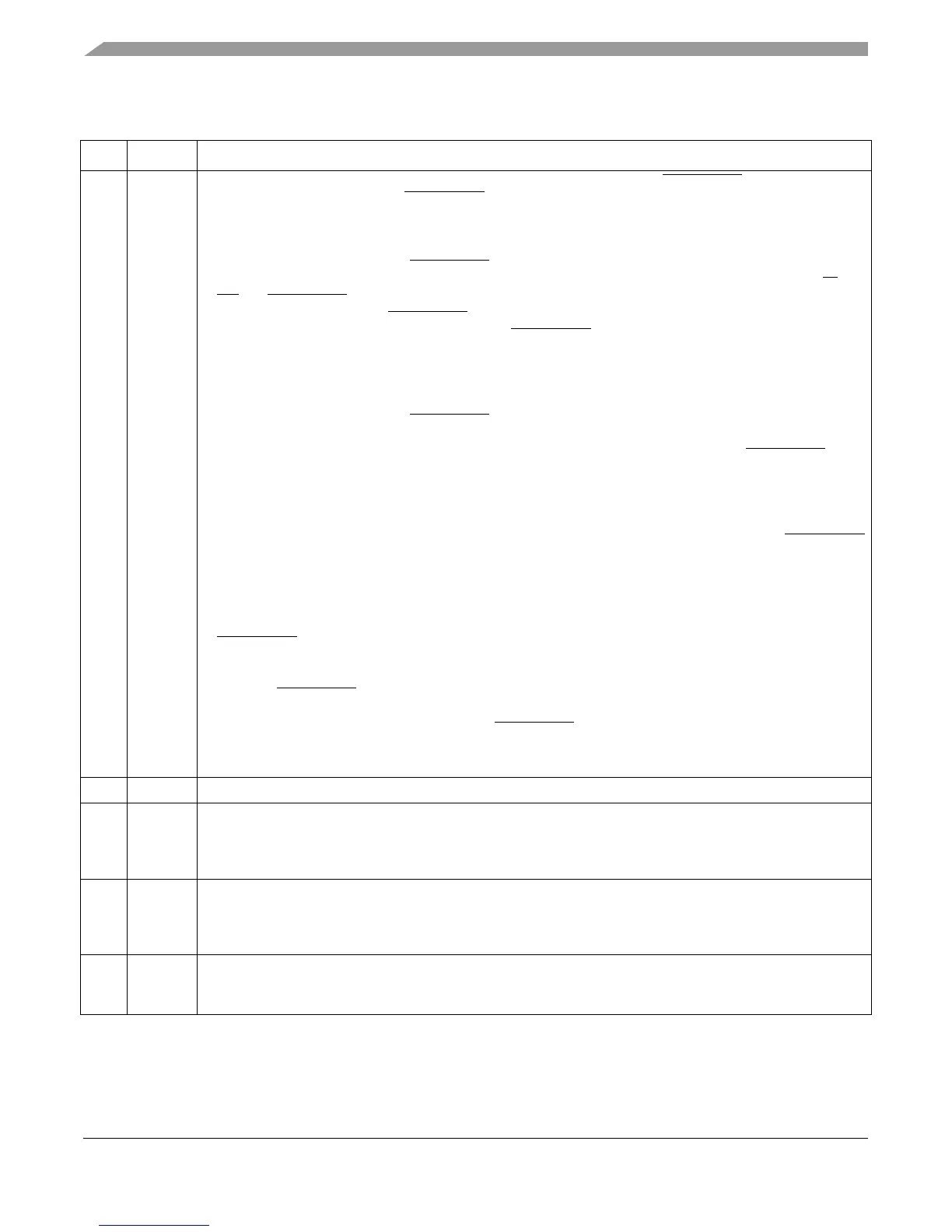

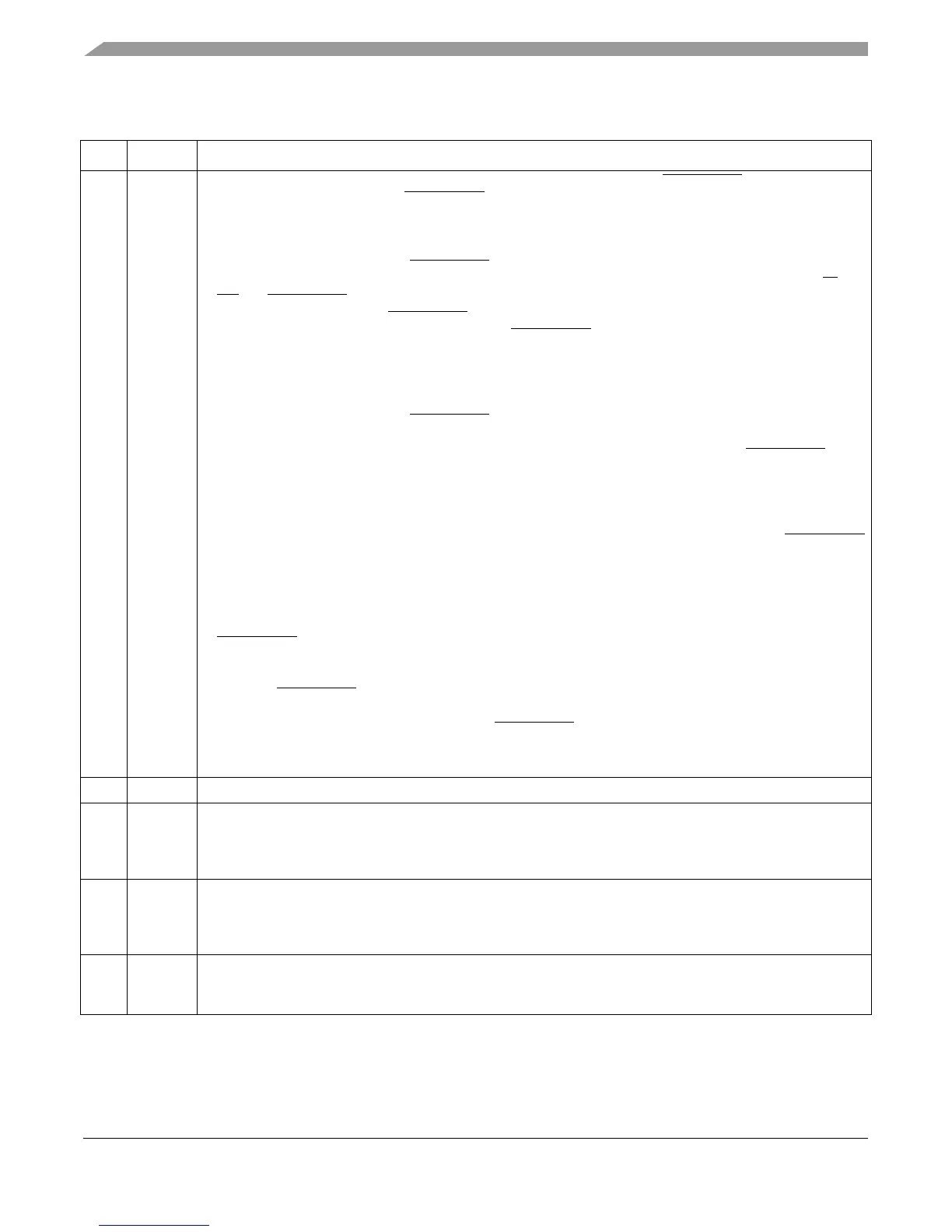

46 RFXE Read fault exception enable. With MSR[ME], controls whether assertion of

core_fault_in

causes a machine

check interrupt. The assertion of

core_fault_in

can result from an L2 multibit ECC error. It can also occur for

a system error if logic on the integrated device signals a fault for a transaction initiated by the core (for

example, a master abort of a PCI transaction). See Section 13.8, “Proper Reporting of Bus Faults,” for

more information.

0 Normal operation. Assertion of

core_fault_in

does not cause a machine check. In normal operation RFXE

should be left clear and an interrupt should be reported by the integrated device (possibly through

int

or

cint

) for

core_fault_in

conditions. If RFXE = 0, it is important that the integrated device be configured to

generate an interrupt when

core_fault_in

is asserted.

1 A machine check can occur due to assertion of

core_fault_in

.

If MSR[ME] = 1 and a fault is signaled, a machine check interrupt occurs.

If MSR[ME] = 0 and a fault is signaled, a checkstop occurs.

Caveat for the e500v1.

CCB transactions that result in

core_fault_in

being asserted may contain bad data. On the e500v1, such

transactions may complete and the core could continue executing with bad data. Note that even if the

peripheral blocks are set up to signal an interrupt to the core for all possible causes of

core_fault_in

, there

is some delay between the completion of the CCB transaction (with potentially bad data) and the

processing of the peripheral block interrupt.Therefore, for the e500v1, if software requires that code

execution stop immediately when a bus fault occurs, RFXE must be set to 1 so that at a minimum, a

machine check exception is taken immediately and processing does not continue with potentially bad data.

However, setting RFXE when a peripheral block is configured to also signal an interrupt for a

core_fault_in

case results in both a machine check interrupt (if MSR[ME] = 0) and potentially an external interrupt

occuring when a bus fault is detected by that peripheral.þIn this case, the machine check interrupt handler

can re-enable external interrupts and wait for the interrupt from the peripheral block, and handle the

condition, before returning from the machine check exception, therefore protecting the system from using

potentially bad data. Note that on the e500v2, the core never completes a CCB transaction for which

core_fault_in is

asserted, so the above precautions regarding execution with bad data do not apply.

RFXE should always be 0 for normal operation for the e500v2; it should be set only if it is necessary that the

assertion of

core_fault_in

generate a machine check or a checkstop because peripherals are not properly

configured to report bus faults. This would typically occur only during software or firmware development.

Note that the L2 cache detects any assertion of

core_fault_in

and ensures that the L2 cache is not corrupted

when data is dropped for this type of transaction.

Machine check generation for bus parity errors is not affected by this bit.

47 — Reserved, should be cleared.

48 R1DPE R1 data bus parity enable. The R1 and R2 data buses are described in Chapter 13, “Core Complex Bus

(CCB).”

0 R1 data bus parity checking disabled

1 R1 data bus parity checking enabled

49 R2DPE R2 data bus parity enable. The R1 and R2 data buses are described in Chapter 13, “Core Complex Bus

(CCB).”

0 R2 data bus parity checking disabled

1 R2 data bus parity checking enabled

50 ASTME Address bus streaming mode enable

0 Address bus streaming mode disabled

1 Address bus streaming mode enabled

Table 2-15. HID1 Field Descriptions (continued)

Bits Name Description

Loading...

Loading...