PowerPC e500 Core Family Reference Manual, Rev. 1

8-6 Freescale Semiconductor

Debug Support

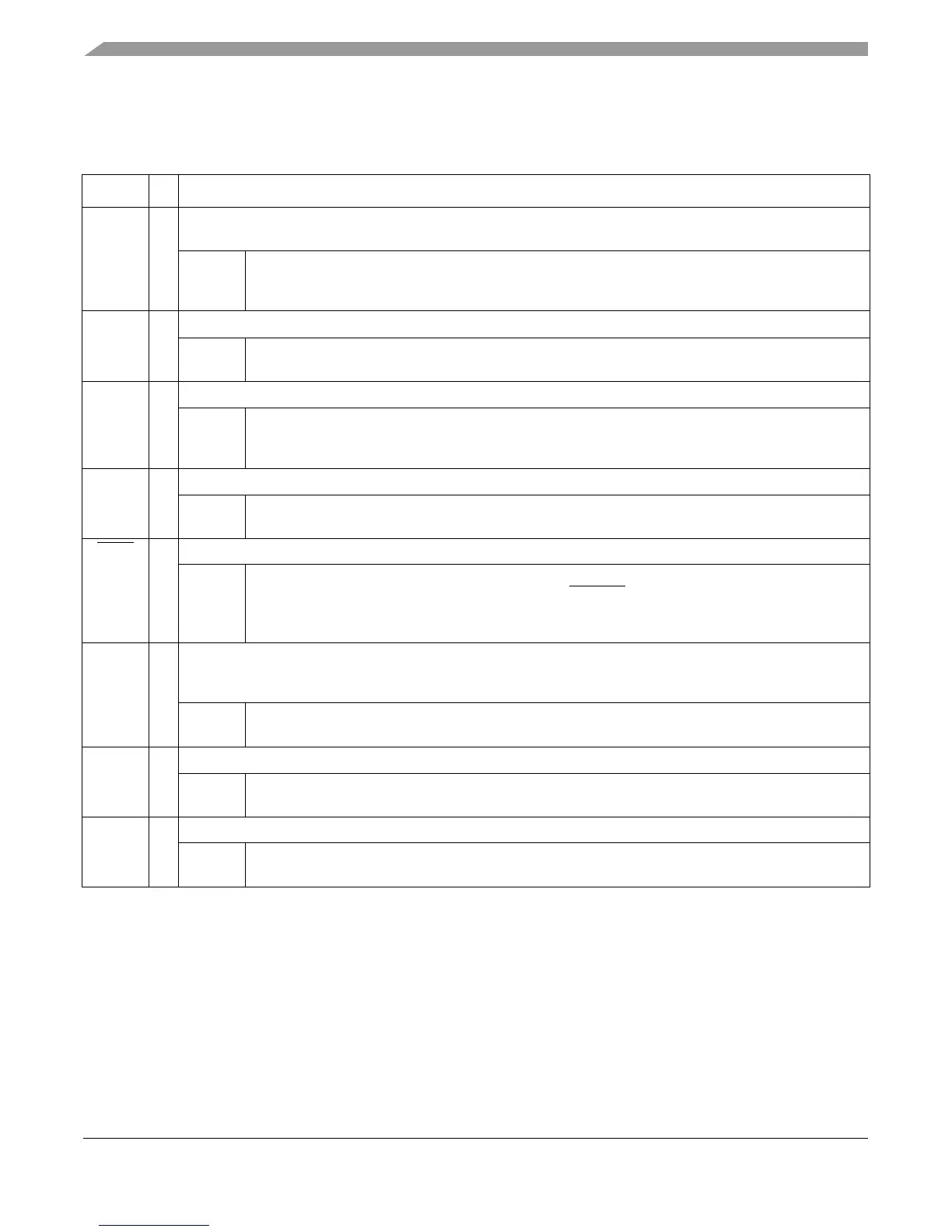

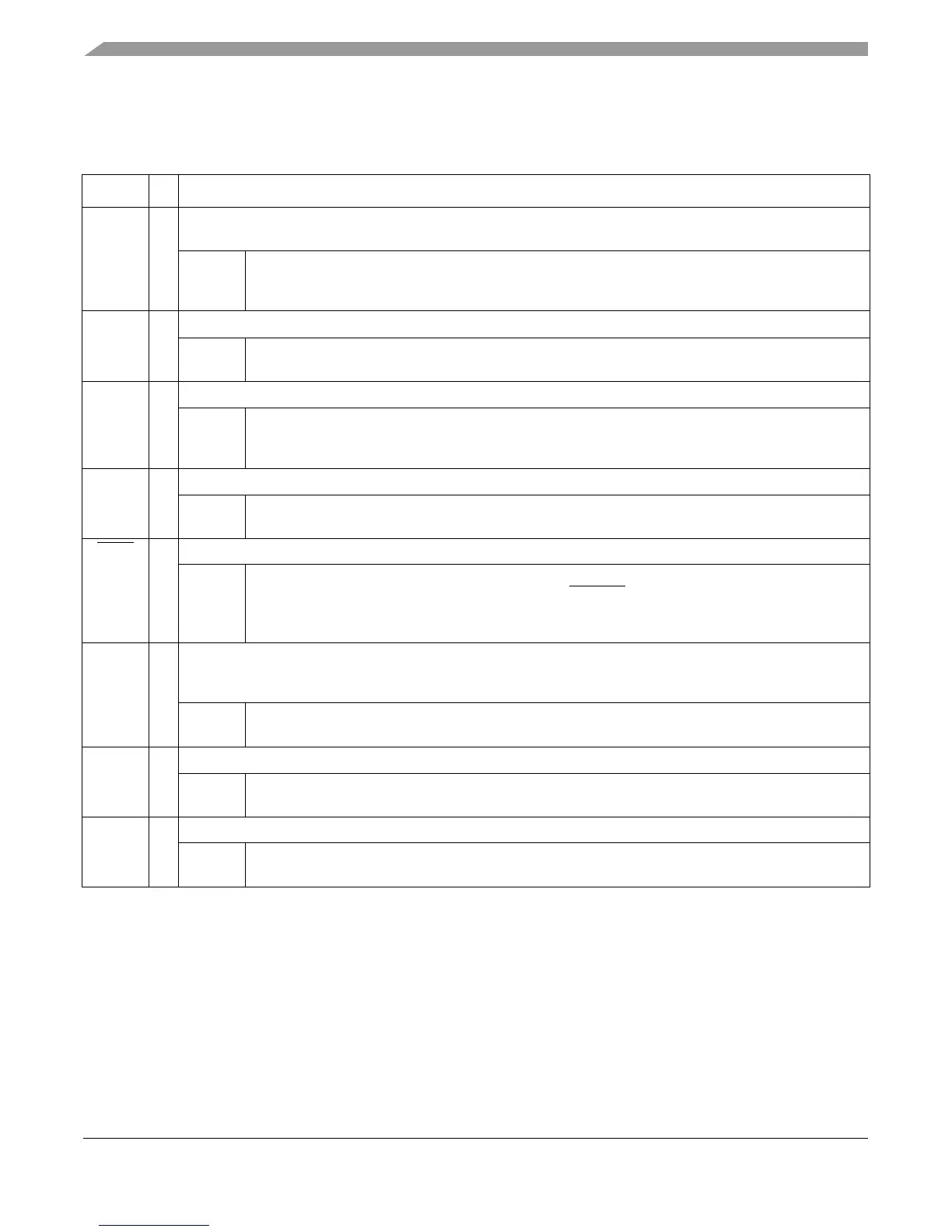

Table 8-5 describes JTAG signals in detail.

8.4 Book E Debug Events

Debug events cause debug exceptions to be recorded in the DBSR (see Section 2.13.2, “Debug

Status Register (DBSR)”). Except for an unconditional debug event, the specific event type must

be enabled by corresponding bits in the debug control registers (DBCR0–DBCR2) for any debug

event to set a DBSR bit and thereby cause a debug exception. Setting a DBSR bit causes a debug

interrupt only if debug interrupts are enabled.

Table 8-5. JTAG Signal Details

Signal I/O Description

TCK I JTAG test clock. Primary clock input for the test logic on the e500. May be asynchronous with respect to all other

core complex clocks.

State

Meaning

Asserted/Negated—This input should be driven by a free-running clock signal. Input signals to the

test access port are sampled on the rising edge of TCK. TAP output signal changes occur on

the falling edge of TCK. The test logic allows TCK to be stopped.

TDI I JTAG test data input. Primary JTAG data input to both scan chain and test control registers.

State

Meaning

Asserted/Negated—The value present on the rising edge of TCK is loaded into the selected JTAG

test instruction or data register.

TDO O JTAG test data output. Primary JTAG data output.

State

Meaning

Asserted/Negated—The contents of the selected internal instruction or data register are shifted out

onto this signal. Valid data appears on the falling edge of TCK. Quiescent except when scanning

of data is in progress.

TMS I JTAG test mode select. Primary JTAG mode control input.

State

Meaning

Asserted/Negated—Decoded by the internal JTAG TAP controller to determine the primary operation

of the test support circuitry.

TRST

I JTAG test reset. JTAG initialization input.

State

Meaning

Asserted—Causes asynchronous initialization of the internal JTAG test access port controller. Must

be asserted sometime during the assertion of HRESET

to properly initialize the JTAG test

access port.

Negated—Indicates normal operation.

TAP_EN I TAP enable. Used by the TAP linking module (TLM) logic external to the core complex to select the core complex

TAP module. When there is no TLM connected to the TAP, the TAP_EN is connected high via an internal pull-up

resistor.

State

Meaning

Asserted—A valid TMS signal is applied to the TAP controller.

Negated—A valid TMS signal is not being applied to the TAP controller.

TDO_EN O TDO enable. Provides feedback to the external TAP linking module logic.

State

Meaning

Asserted—Valid data is available on TDO.

Negated—Value of TDO is meaningless.

TLMSEL O TLM selected. Provides feedback to the external TAP linking module logic.

State

Meaning

Asserted—The core complex is currently executing a TLM TAP instruction.

Negated—The core complex is not currently executing a TLM TAP instruction

Loading...

Loading...