Instruction Model

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 3-21

The following notes describe the e500 implementation of integer load instructions:

• Book E cautions programmers that some implementations of the architecture can execute

the load half algebraic (lha, lhax) instructions with greater latency than other types of load

instructions. This is not the case for the e500; these instructions operate with the same

latency as other load instructions.

• Book E cautions programmers that some implementations can run the load/store

byte-reverse (lhbrx, lbrx, sthbrx, stwbrx) instructions with greater latency than other

types of load/store instructions. This is not the case for the e500. These instructions operate

with the same latency as the other load/store instructions.

• The Book E architecture defines lwarx and stwcx. as a way to update memory atomically.

In the e500, reservations are made on behalf of aligned 32-byte sections of the memory

address space. Executing lwarx and stwcx. to a page marked write-through causes a data

storage interrupt if the page is marked cacheable write-through (WIM = 10x), but as with

other memory accesses, data storage interrupts can result for other reasons such as

protection violations or page faults.

3.3.1.2.4 Integer Store Instructions

For integer store instructions, the rS contents are stored into the byte, half word, word, or double

word in memory addressed by the EA (effective address). Many store instructions have an update

form in which rA is updated with the EA. For these forms, the following rules apply:

•If rA ≠ 0, the effective address is placed into rA.

• If rS=rA, the contents of register rS are copied to the target memory element and the

generated EA is placed into rA (rS).

The Book E architecture defines store with update instructions with rA = 0 as an invalid form. In

addition, it defines integer store instructions with the CR update option enabled (Rc field, bit 31,

in the instruction encoding = 1) to be an invalid form. Table 3-12 summarizes integer store

instructions.

Load Word and Zero Indexed lwzx rD,rA,rB

Load Word and Zero with Update lwzu rD,d(rA)

Load Word and Zero with Update Indexed lwzux rD,rA,rB

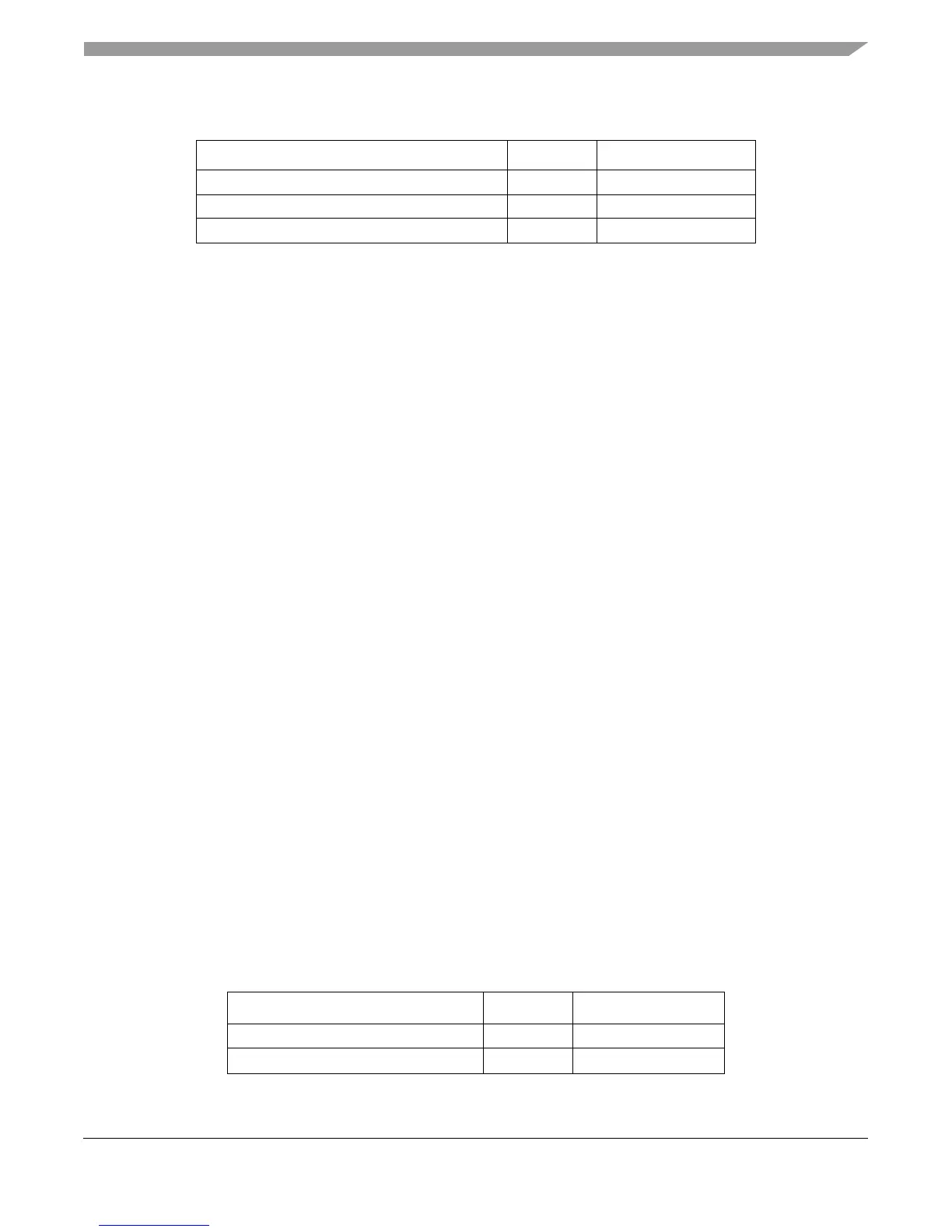

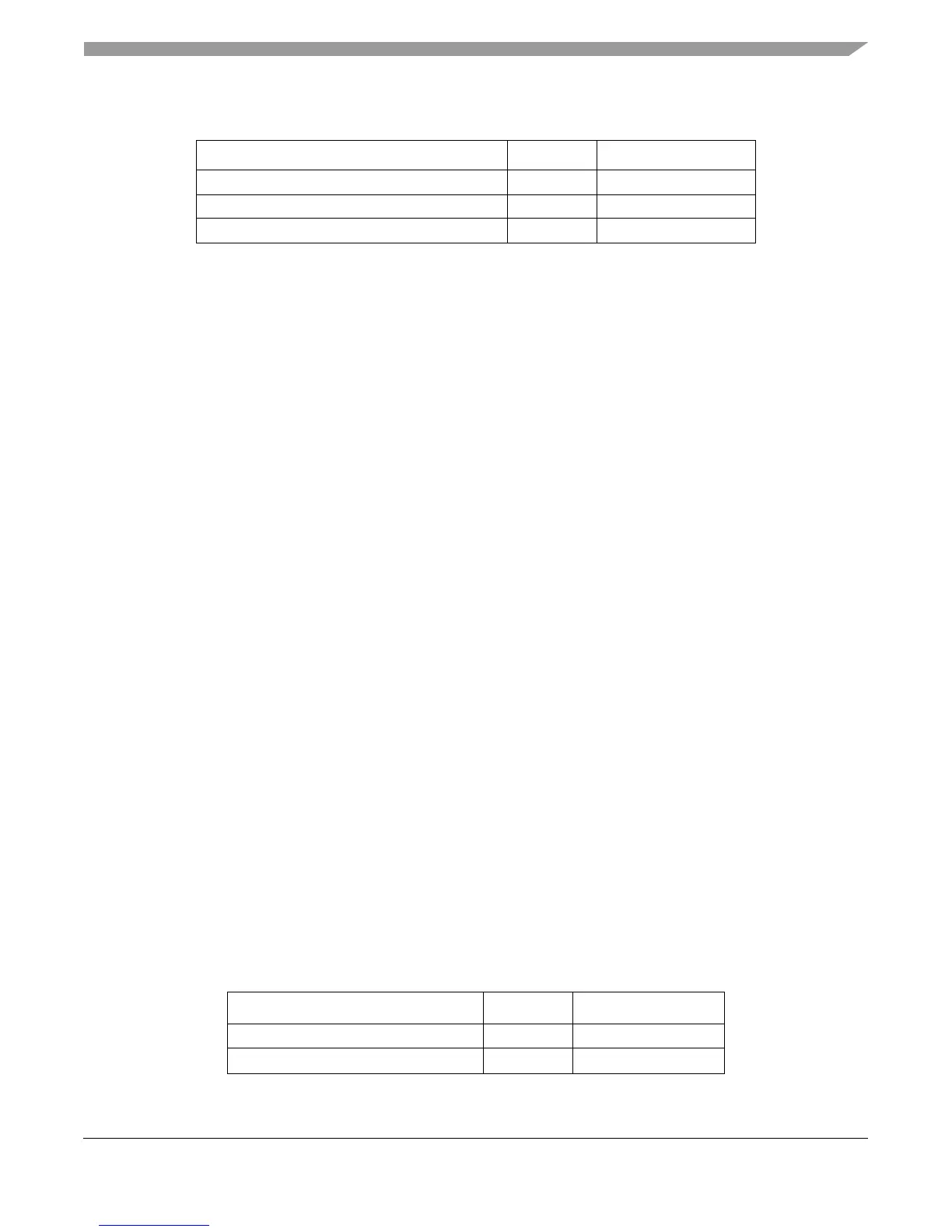

Table 3-12. Integer Store Instructions

Name Mnemonic Syntax

Store Byte stb rS,d(rA)

Store Byte Indexed stbx rS,rA,rB

Table 3-11. Integer Load Instructions (continued)

Name Mnemonic Syntax

Loading...

Loading...