Register Model

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 2-55

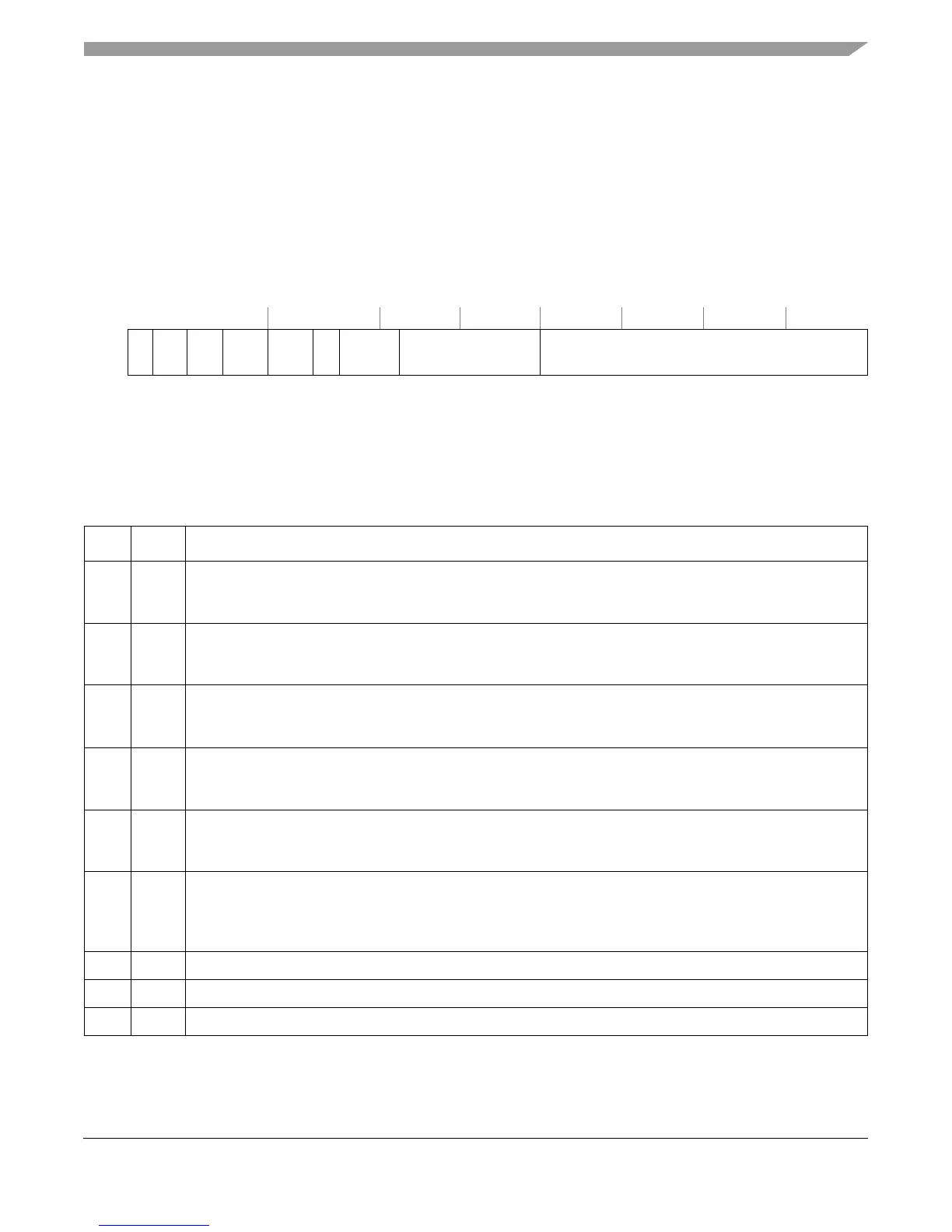

2.15.3 Local Control A Registers (PMLCa0–PMLCa3)

The local control A registers 0–3 (PMLCa0–PMLCa3), shown in Figure 2-40, function as event

selectors and give local control for the corresponding performance monitor counters. PMLCa

works with the corresponding PMLCb register.

Table 2-39 describes the PMLCa fields.

PMLCa0 (PMR144)

PMLCa1 (PMR145)

PMLCa2 (PMR146)

PMLCa3 (PMR147)

UPMLCa0 (PMR128)

UPMLCa1 (PMR129)

UPMLCa2 (PMR130)

UPMLCa3 (PMR131)

Access: PMLCa0–PMLCa3: Supervisor-only

UPMLCa0–UPMLCa3: Supervisor/user read-only

32 33 34 35 36 37 38 40 41 47 48 63

R

FC FCS FCU FCM1 FCM0 CE — EVENT —

W

Reset All zeros

Figure 2-40. Local Control A Registers (PMLCa0–PMLCa3)/

User Local Control A Registers (UPMLCa0–UPMLCa3)

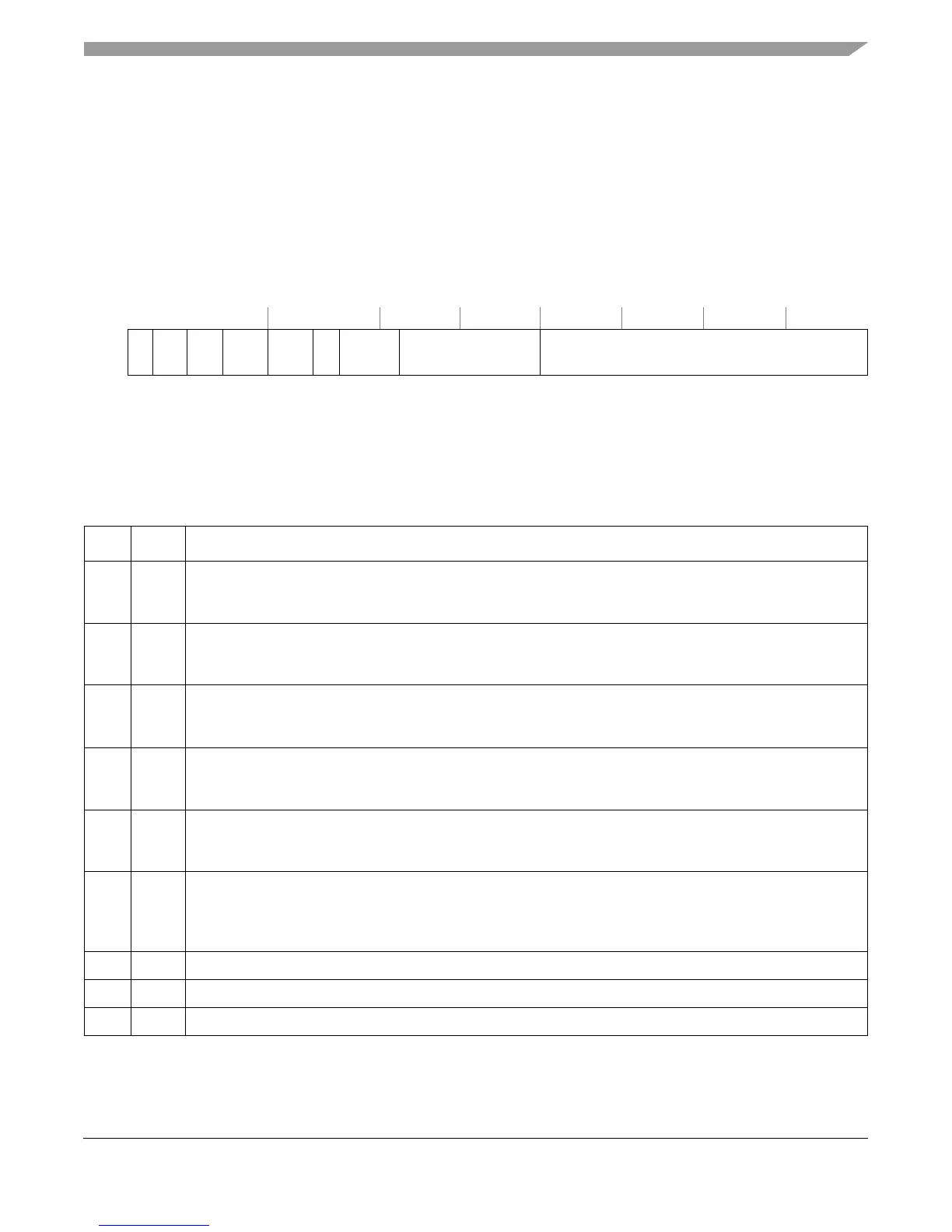

Table 2-39. PMLCa0–PMLCa3 Field Descriptions

Bits Name Description

32 FC Freeze counter

0 The PMC is incremented (if permitted by other PM control bits).

1 The PMC is not incremented.

33 FCS Freeze counter in supervisor state

0 The PMC is incremented (if permitted by other PM control bits).

1 The PMC is not incremented if MSR[PR] = 0.

34 FCU Freeze counter in user state

0 The PMC is incremented (if permitted by other PM control bits).

1 The PMC is not incremented if MSR[PR] = 1.

35 FCM1 Freeze counter while mark = 1

0 The PMC is incremented (if permitted by other PM control bits).

1 The PMC is not incremented if MSR[PMM] = 1.

36 FCM0 Freeze counter while mark = 0

0 The PMC is incremented (if permitted by other PM control bits).

1 The PMC is not incremented if MSR[PMM] = 0.

37 CE Condition enable

0PMC

x

overflow conditions cannot occur. (PMC

x

cannot cause interrupts, cannot freeze counters.)

1 Overflow conditions occur when the most-significant-bit of PMC

x

is equal to one.

It is recommended that CE be cleared when counter PMC

x

is selected for chaining.

38–40 — Reserved, should be cleared.

41–47 EVENT Event selector. Up to 128 events selectable.

48–63 — Reserved, should be cleared.

Loading...

Loading...