PowerPC e500 Core Family Reference Manual, Rev. 1

8-2 Freescale Semiconductor

Debug Support

In addition, Book E defines the debug enable bit in the machine state register, MSR[DE], which

must be set for debug events to cause debug interrupts to be taken. This bit is described in

Section 2.5.1, “Machine State Register (MSR).” Note that debug interrupts are not affected by the

critical enable bit (MSR[CE]).

8.2.2 Instruction Set

The SPRs listed in Table 8-1 are accessed by the mtspr and mfspr instructions. The MSR is

accessed with mtmsr and mfmsr instructions. Also, the MSR is updated with the contents of

CSRR1 when an rfmci instruction is executed, typically at the end of an interrupt handler.

8.2.3 Debug Interrupt Model

Book E defines the debug interrupt as a critical class interrupt. Critical class interrupts use a

separate pair of save and restore registers (CSRR0 and CSRR1) whose contents are updated when

a critical interrupt is taken. The Return from Critical Interrupt (rfci) instruction uses these registers

to restore state at the end of the interrupt handler. Debug interrupts do not affect the save/restore

registers, SRR0 and SRR1, and CSRR registers are not affected by the Return from Interrupt (rfi)

instruction.

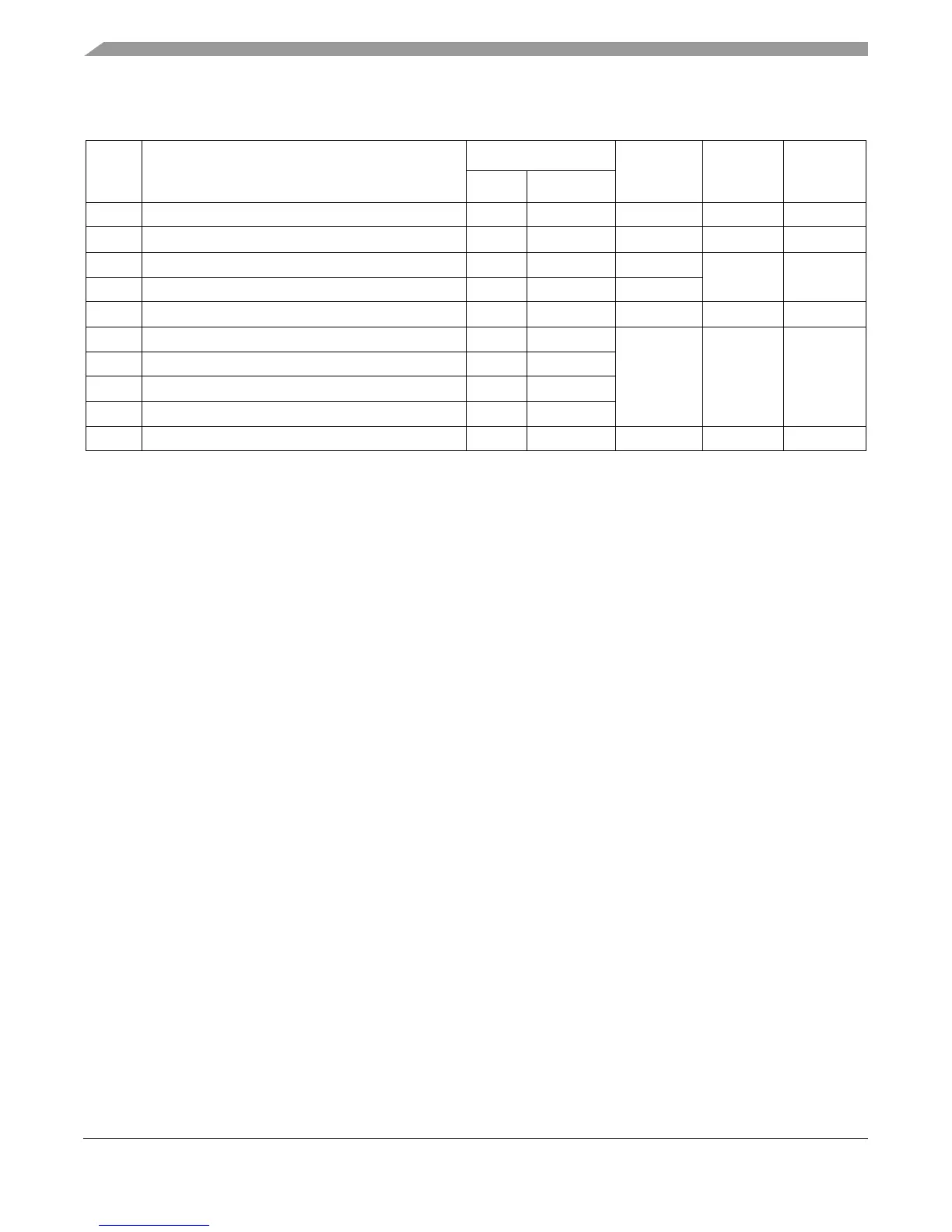

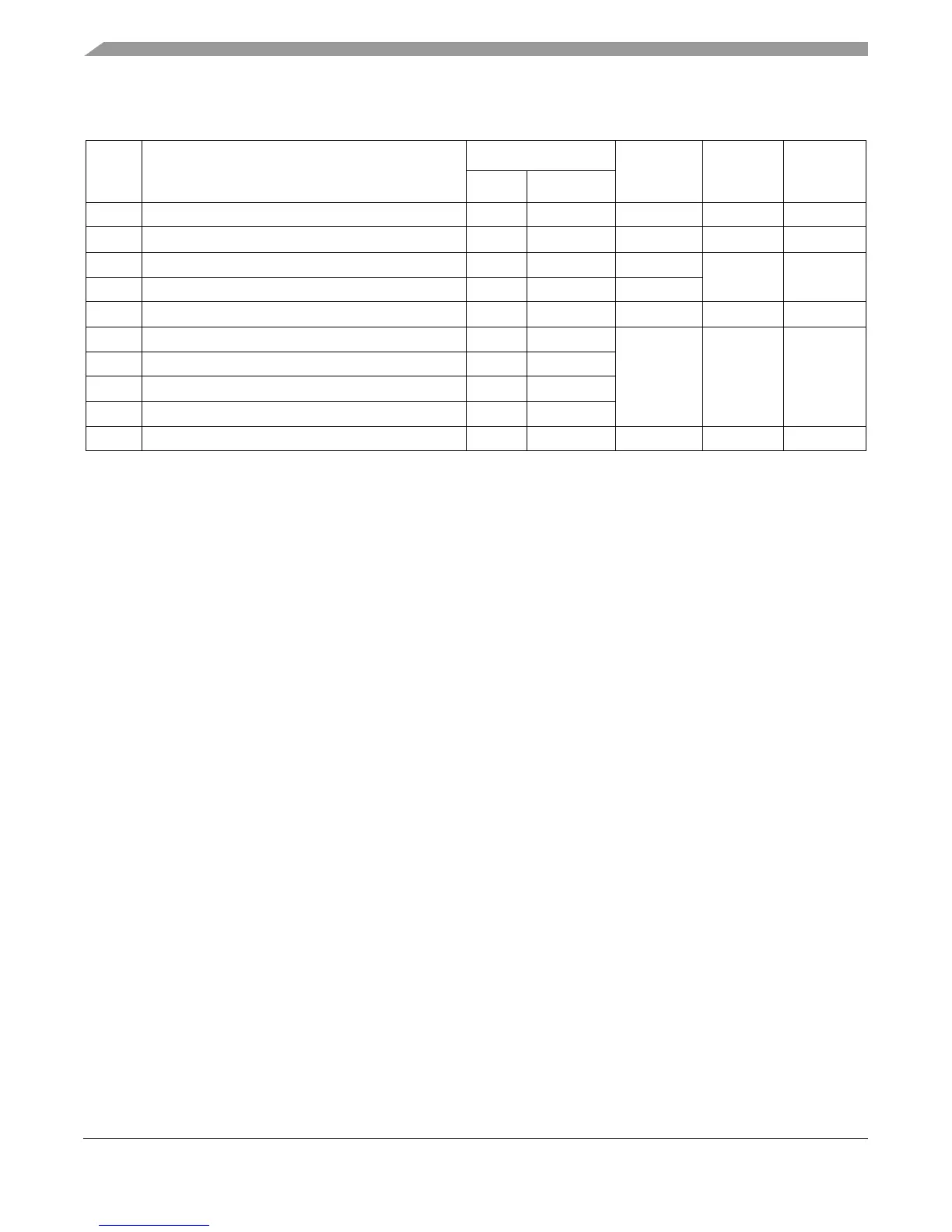

DBSR Debug status register 304 01001 10000 Read/Clear

2

Ye s 2.13.2/2-47

DEAR Data exception address register 61 00001 11101 R/W Yes 2.7.1.3/2-18

DEC Decrementer 22 00000 10110 R/W Yes 2.6.4/2-16

DECAR Decrementer auto-reload 54 00001 10110 Write-only

ESR Exception syndrome register 62 00001 11110 R/W Yes 2.7.1.6/2-20

IAC1

1

Instruction address compare 1 312 01001 11000 R/W Yes 2.13.3/2-48

IAC2

1

Instruction address compare 2 313 01001 11001

IAC3 Instruction address compare 3 (not implemented) 314 01001 11010

IAC4 Instruction address compare 4 (not implemented) 315 01001 11011

IVOR15 Debug interrupt offset 415 01100 11111 R/W Yes 2.7.1.5/2-19

1

Address comparisons only compare effective, not real, addresses.

2

The DBSR is read using mfspr. It cannot be directly written to. Instead, DBSR bits corresponding to 1 bits in the GPR can be

cleared using mtspr.

Table 8-1. Debug SPRs (continued)

SPR Name

Defined SPR Number

Access

Supervisor

Only

Section/

Page

Decimal Binary

Loading...

Loading...