PowerPC e500 Core Family Reference Manual, Rev. 1

3-40 Freescale Semiconductor

Instruction Model

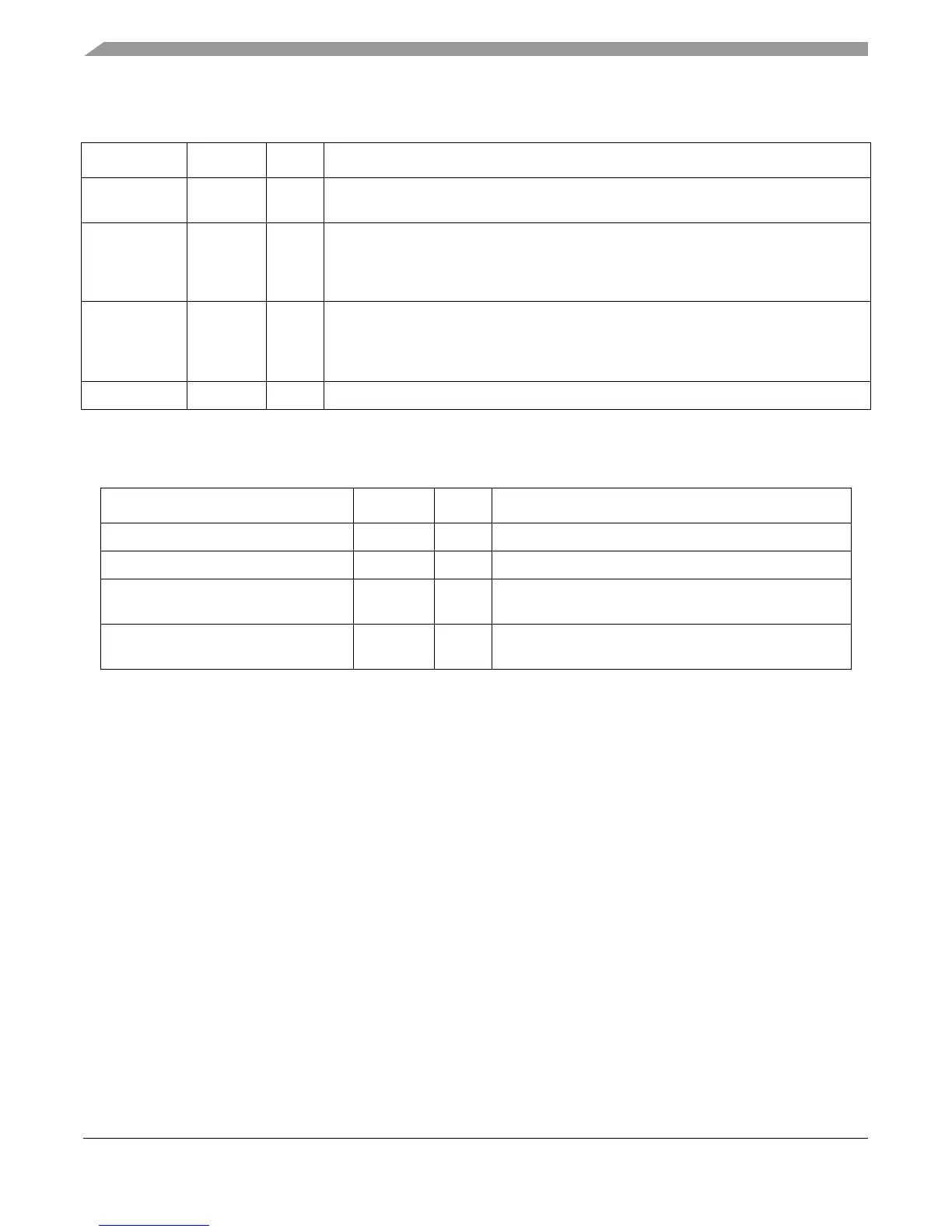

Table 3-28 lists instructions for accessing the MSR.

Certain encodings of the SPR field of mtspr and mfspr instructions (shown in Table 3-22) provide

access to supervisor-level SPRs. Table 3-23 lists encodings for architecture-defined SPRs.

Encodings for e500-specific, supervisor-level SPRs are listed in Table 3-24. Simplified

mnemonics are provided for mtspr and mfspr. See the EREF for more information on context

synchronization requirements when altering certain SPRs.

3.3.2.2 Supervisor-Level Memory Control Instructions

Memory control instructions include the following:

• Cache management instructions (supervisor-level and user-level)

• Translation lookaside buffer management instructions

This section describes supervisor-level memory control instructions. Section 3.3.1.8, “Memory

Control Instructions,” describes user-level memory control instructions.

3.3.2.2.1 Supervisor-Level Cache Instruction

Table 3-29 lists the only supervisor-level cache management instruction.

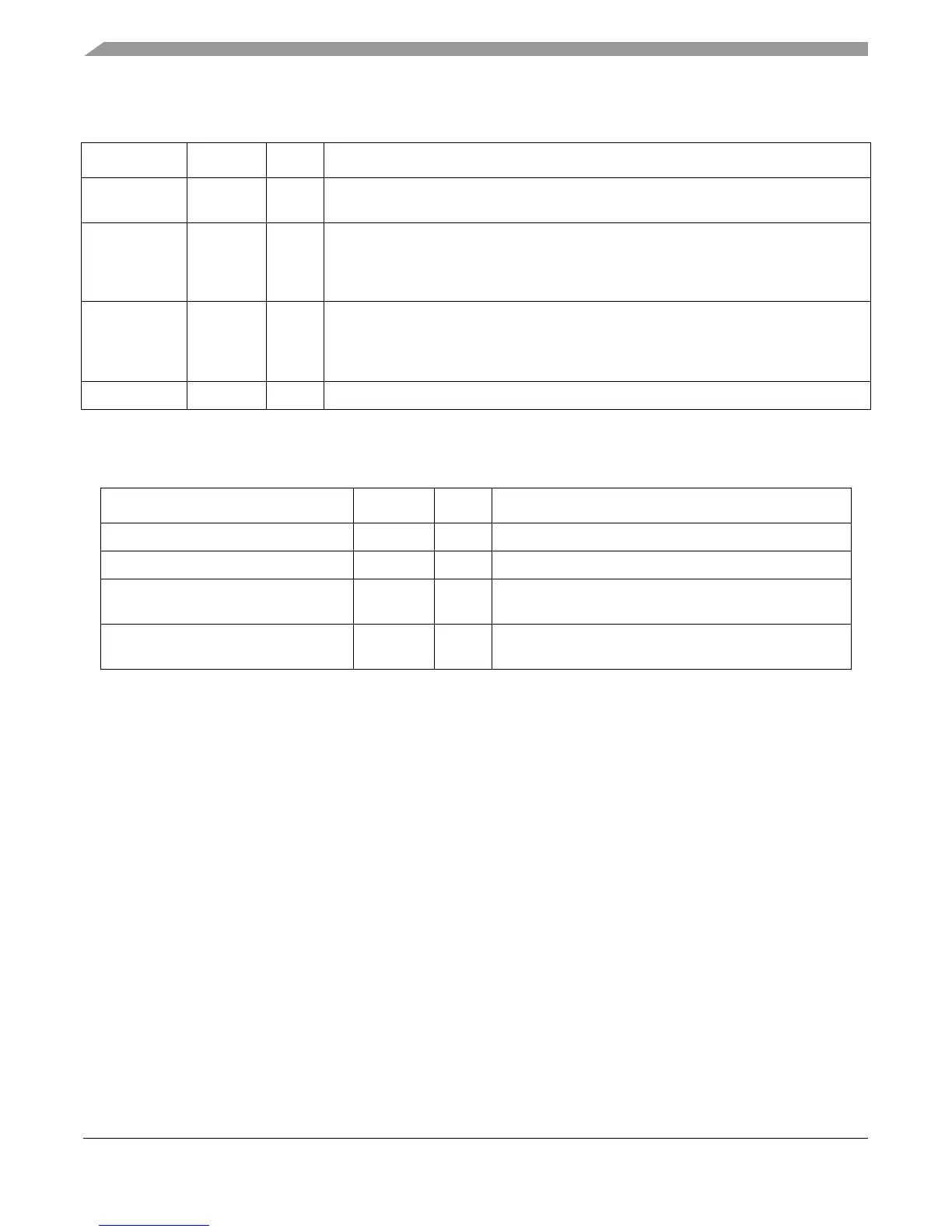

Table 3-27. System Linkage Instructions—Supervisor-Level

Name Mnemonic Syntax Implementation Notes

Return from

Interrupt

rfi — rfi is context-synchronizing, which for the e500 means it works its way to the final execute

stage, updates architected registers, and redirects the instruction flow.

Return from

Machine Check

Interrupt

rfmci — (e500-specific) When rfmci is executed, the values in the machine check interrupt save

and restore registers (MCSRR0 and MCSRR1) are restored. rfmci is

context-synchronizing; it works its way to the final execute stage, updates architected

registers, and redirects instruction flow.

Return from

Critical Interrupt

rfci — When rfci executes, the values in the critical interrupt save and restore registers (CSRR0

and CSRR1) are restored. rfci is context-synchronizing, which for the e500 means it

works its way to the final execute stage, updates architected registers, and redirects the

instruction flow.

System Call sc — The sc instruction is context-synchronizing.

Table 3-28. Move to/from Machine State Register Instructions

Name Mnemonic Syntax Description

Move from Machine State Register mfmsr rD —

Move to Machine State Register mtmsr rS —

Write MSR External Enable wrtee rS Bit 48 of the contents of rS is placed into MSR[EE]. No

other MSR bits are affected.

Write MSR External Enable Immediate wrteei E The value specified in the E field is placed into MSR[EE].

No other MSR bits are affected.

Loading...

Loading...