Core Complex Overview

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 1-25

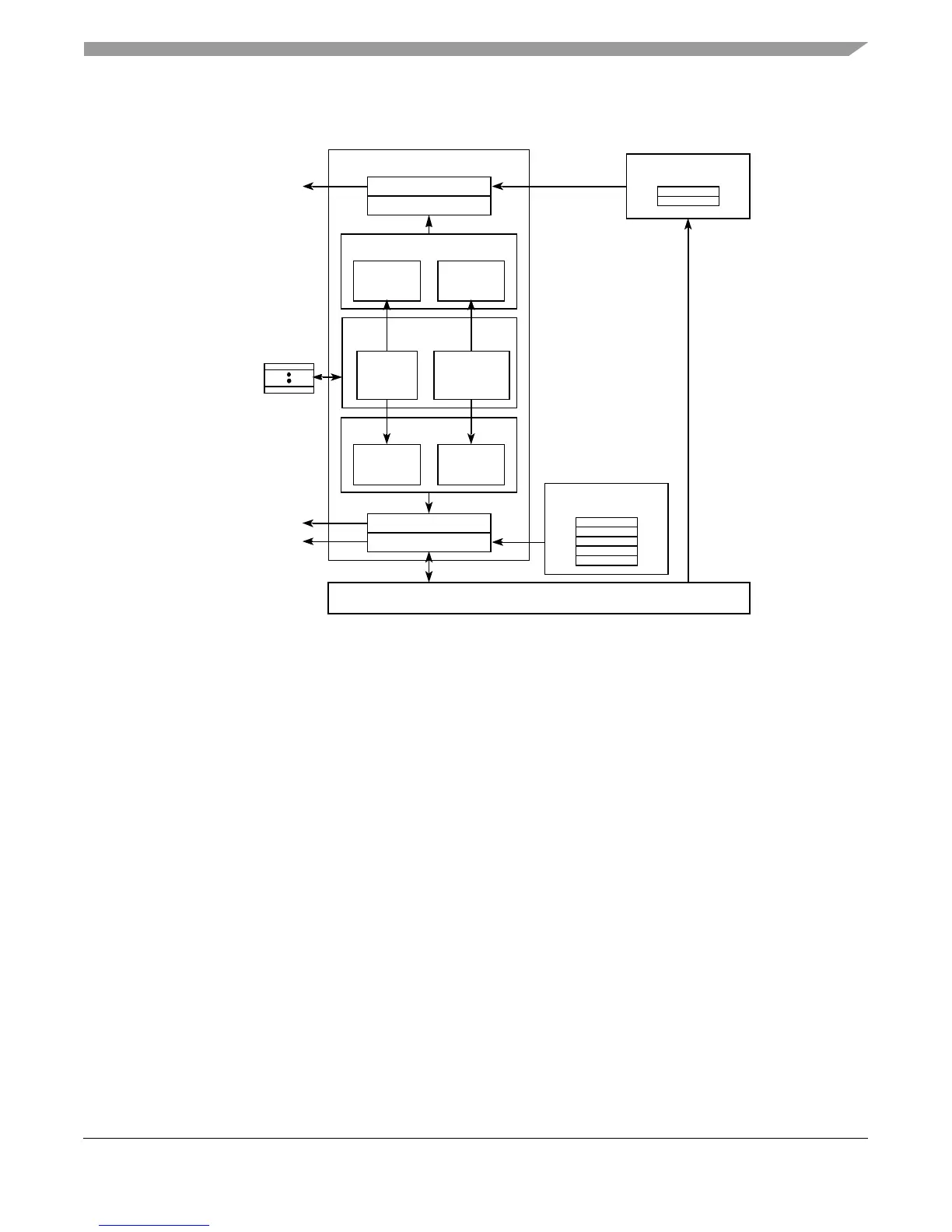

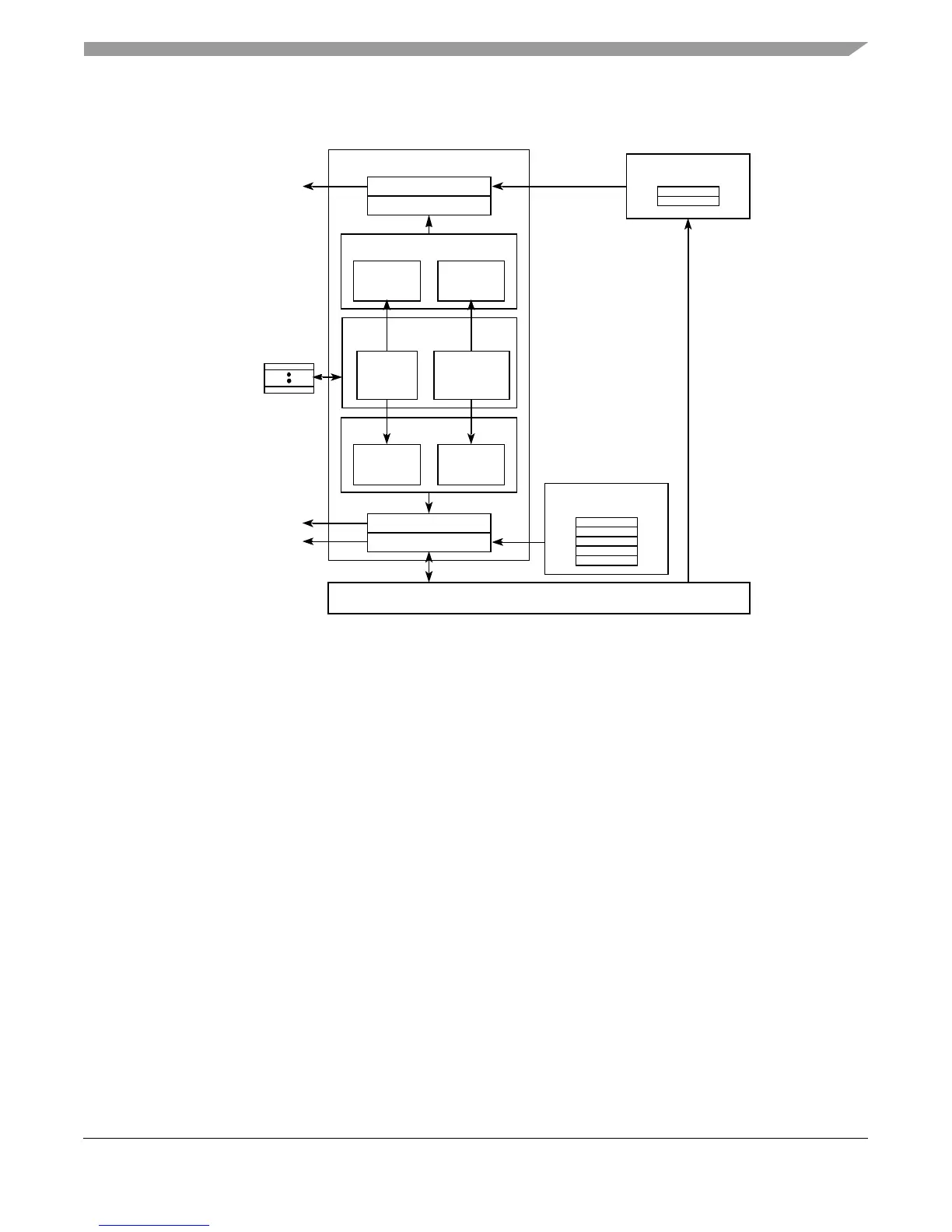

This two-level structure is shown in Figure 1-8.

Figure 1-8. MMU Structure

Level-1 MMUs have the following features:

• Four-entry, fully associative TLB array that supports all nine page sizes

• 64-entry, 4-way set-associative TLB 4-Kbyte array that supports 4-Kbyte pages only

• Hardware partially managed by L2 MMU

• Supports snooping of TLBs by both internal and external tlbivax instructions

The level-2 MMU has the following features:

• A 16-entry, fully associative L2 TLB array (TLB1) that supports all nine variable page sizes

• TLB array (TLB0) that supports only 4-Kbyte pages, as follows:

— e500v1—256-entry, 2-way set-associative TLB array

— e500v2—512-entry, 4-way set-associative TLB array

• Hardware assist for TLB miss exceptions

• Software managed by tlbre, tlbwe, tlbsx, tlbsync, tlbivax, and mtspr instructions

• Supports snooping of TLB by both internal and external tlbivax instructions

L2 MMUs

256/512-Entry

TLB Array

16-Entry

(TLB0)

TLB Array

(TLB1)

Unified

L1 Data MMU

64-Entry

D-L1TLB4K

4-Entry

D-L1VSP

L1 Instruction MMU

64-Entry

I-L1TLB4K

4-Entry

I-L1VSP

32-Kbyte I-Cache

Memory Unit

Ta gs

Ta gs

32-Kbyte D-Cache

MAS

Registers

To instruction unit

Instruction Line

FIll Buffer

To load/store unit

Core Interface

Data Line

FIll Buffer

Loading...

Loading...