PowerPC e500 Core Family Reference Manual, Rev. 1

5-32 Freescale Semiconductor

Interrupts and Exceptions

5.7.15.2 Embedded Floating-Point Data Interrupt

An embedded floating-point data interrupt is generated in the following cases:

• SPEFSCR[FINVE] = 1 and either SPEFSCR[FINVH,FINV] = 1

• SPEFSCR[FDBZE] = 1and either SPEFSCR[FDBZH,FDBZ] = 1

• SPEFSCR[FUNFE] = 1 and either SPEFSCR[FUNFH,FUNF] = 1

• SPEFSCR[FOVFE] = 1 and either SPEFSCR[FOVFH,FOVF] = 1

Note that although SPEFSCR status bits can be updated by using mtspr, interrupts occur only if

they are set as the result of an arithmetic operation.

When an embedded floating-point data interrupt occurs, the processor suppresses execution of the

instruction causing the interrupt. Table 5-30 shows register settings.

Instruction execution resumes at address IVPR[32–47] || IVOR33[48–59] || 0b0000.

5.7.15.3 Embedded Floating-Point Round Interrupt

The embedded floating-point round interrupt is taken on any of the following conditions:

• SPEFSCR[FINXE] = 1 and any of the SPEFSCR[FGH,FXH,FG,FX] bits = 1

• SPEFSCR[FRMC] = 0b10 (+∞)

• SPEFSCR[FRMC] = 0b11 (–∞)

Note that although these SPEFSCR status bits can be updated by using an mtspr[SPEFSCR],

interrupts occur only if they are set as the result of an arithmetic operation.

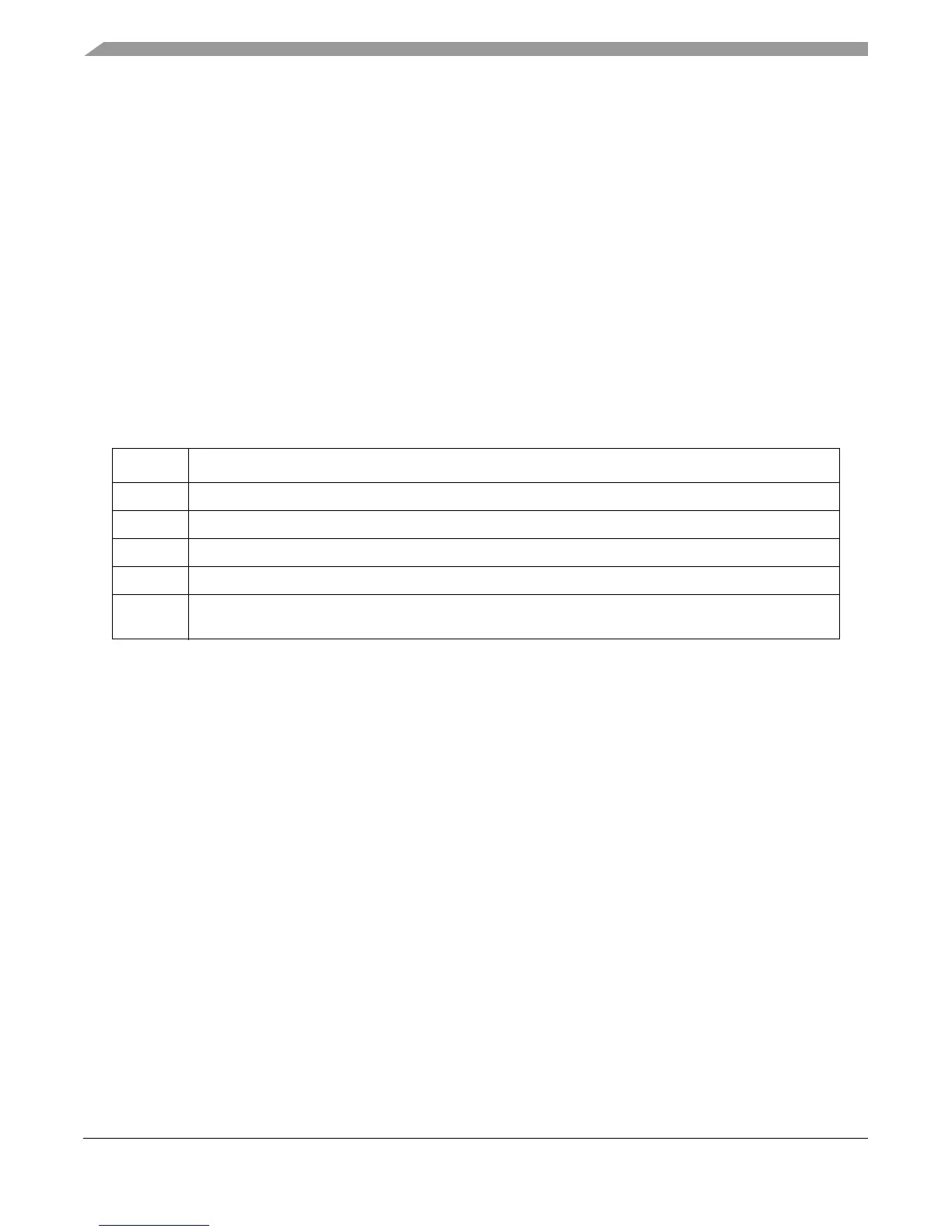

Table 5-30. Embedded Floating-Point Data Interrupt Register Settings

Register Setting

SRR0 Set to the effective address of the instruction causing the interrupt.

SRR1 Set to the MSR contents at the time of the interrupt.

MSR CE, ME, and DE are unchanged. All other bits are cleared.

ESR SPE (bit 24) is set. All other ESR bits are cleared.

SPEFSCR One or more of the FINVH, FINV, FDBZH, FDBZ, FUNFH, FUNF, FOVFH, or FOVF bits are set to indicate

the interrupt type.

Loading...

Loading...