Simplified Mnemonics for PowerPC Instructions

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor C-9

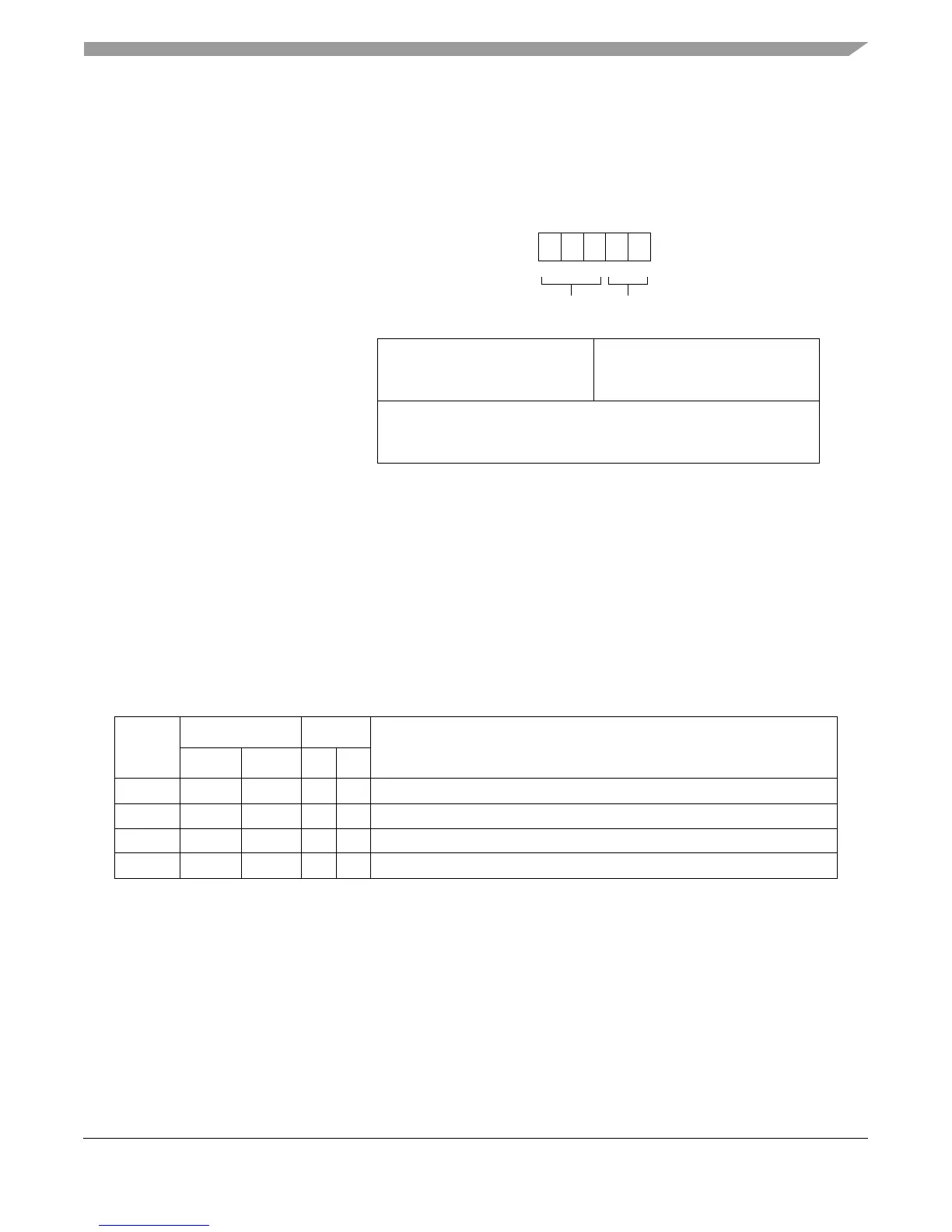

replaced by a crS operand. To understand this, it is useful to view the BI operand as comprised of

two parts. As Figure C-3 shows, BI[0–2] indicates the CR field and BI[3–4] represents the

condition to test.

Figure C-3. BI Field (Bits 11–14 of the Instruction Encoding)

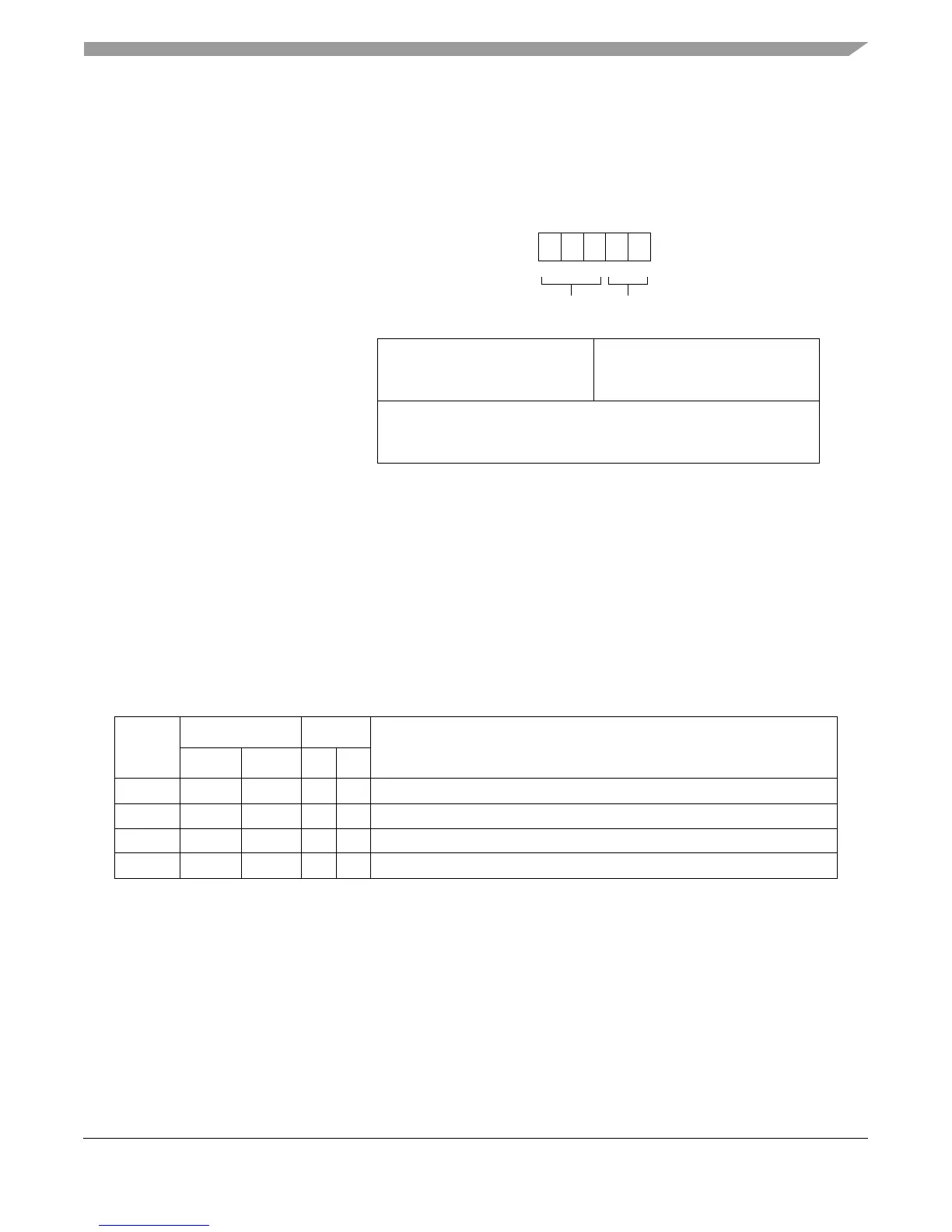

Integer record-form instructions update CR0, as described in Table C-7.

C.4.4.1.1 Specifying a CR Bit

Note that the AIM version the PowerPC architecture numbers CR bits 0–31 and Book E numbers

them 32–63. However, no adjustment is necessary to the code; in Book E devices, 32 is

automatically added to the BI value, as shown in Table C-7 and Table C-8.

Some simplified mnemonics incorporate only the BO field (as described Section C.4.2,

“Eliminating the BO Operand”). If one of these simplified mnemonics is used and the CR must be

accessed, the BI operand can be specified either as a numeric value or by using the symbols in

Table C-8.

Compare word instructions (described in Section C.5, “Compare Word Simplified Mnemonics”),

move to CR instructions, and others can also modify CR fields, so CR0 and CR1 may hold values

that do not adhere to the meanings described in Table C-7. CR logical instructions, described in

Section C.6, “Condition Register Logical Simplified Mnemonics,” can update individual CR bits.

Table C-7. CR0 and CR1 Fields as Updated by Integer Instructions

CR

n

Bit

CR Bits BI

Description

AIM Book E 0–2 3–4

CR0[0] 0 32 000 00 Negative (LT)—Set when the result is negative.

CR0[1] 1 33 000 01 Positive (GT)—Set when the result is positive (and not zero).

CR0[2] 2 34 000 10 Zero (EQ)—Set when the result is zero.

CR0[3] 3 35 000 11 Summary overflow (SO). Copy of XER[SO] at the instruction’s completion.

01234

BI[0–2] specifies CR field, CR0–CR7. BI[3–4] specifies one of the

4 bits in a CR field. (LT, GT, EQ,SO)

Simplified mnemonics based on CR

conditions but not CTR values—BO = 12

(branch if true) and BO = 4 branch if false)

Specified by a separate,

reduced BI operand (crS)

Incorporated into the simplified

mnemonic.

Standard branch mnemonics and

simplified mnemonics based on CTR

values

The BI operand specifies the entire 5-bit field. If CR0 is used, the bit can

be identified by LT, GT, EQ, or SO. If CR1–CR7 are used, the form

4 * crS + LT|GT|EQ|SO can be used.

BI Opcode Field

Loading...

Loading...