PowerPC e500 Core Family Reference Manual, Rev. 1

3-58 Freescale Semiconductor

Instruction Model

3.8.1.4 Embedded Floating-Point APU Instructions

The vector and scalar SPFP APUs perform floating-point operations on single-precision operands.

These operations are IEEE 754–compliant with software exception handlers and offer a simpler

exception model than the floating-point instructions defined by the PowerPC ISA. Instead of

FPRs, these instructions use GPRs to offer improved performance for converting between

floating-point, integer, and fractional values. Sharing GPRs allows vector floating-point

instructions to use SPE load and store instructions.

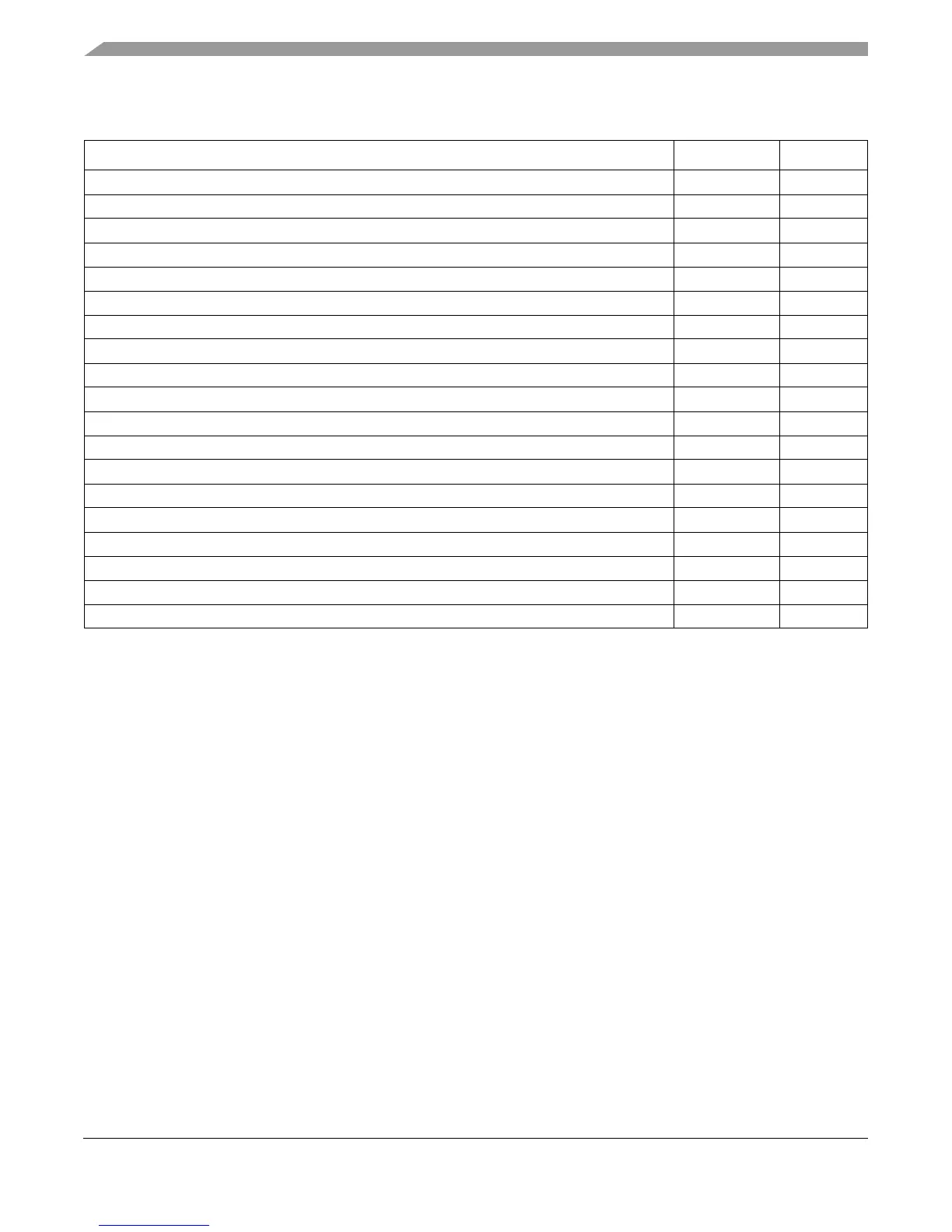

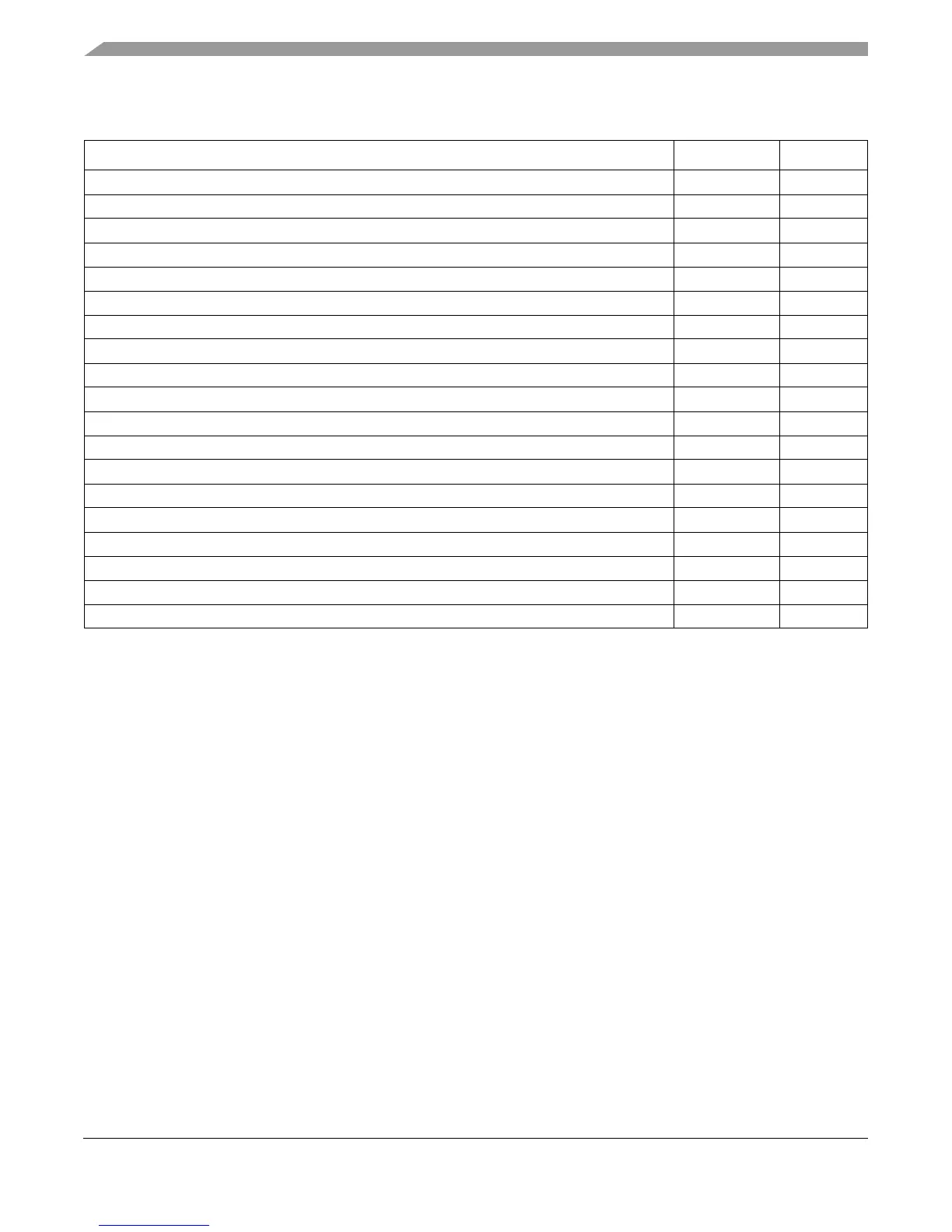

Vector Store Double of Four Half Words evstdh rS,d(rA)

Vector Store Double of Four Half Words Indexed evstdhx rS,rA,rB

Vector Store Double of Two Words evstdw rS,d(rA)

Vector Store Double of Two Words Indexed evstdwx rS,rA,rB

Vector Store Word of Two Half Words from Even evstwhe rS,d(rA)

Vector Store Word of Two Half Words from Even Indexed evstwhex rS,rA,rB

Vector Store Word of Two Half Words from Odd evstwho rS,d(rA)

Vector Store Word of Two Half Words from Odd Indexed evstwhox rS,rA,rB

Vector Store Word of Word from Even evstwwe rS,d(rA)

Vector Store Word of Word from Even Indexed evstwwex rS,rA,rB

Vector Store Word of Word from Odd evstwwo rS,d(rA)

Vector Store Word of Word from Odd Indexed evstwwox rS,rA,rB

Vector Subtract from Word evsubfw rD,rA,rB

Vector Subtract Immediate from Word evsubifw rD,UIMM,rB

Vector Subtract Signed, Modulo, Integer to Accumulator Word evsubfsmiaaw rD,rA

Vector Subtract Signed, Saturate, Integer to Accumulator Word evsubfssiaaw rD,r

A

Vector Subtract Unsigned, Modulo, Integer to Accumulator Word evsubfumiaaw rD,rA

Vector Subtract Unsigned, Saturate, Integer to Accumulator Word evsubfusiaaw rD,rA

Vector XOR evxor rD,rA,rB

1

These instructions are also used by the vector and double-precision scalar floating-point APUs.

2

The architecture specifies that if the final result cannot be represented in 64 bits, SPEFSCR[OV] should be set (along with the

SOV bit, if it is not already set). The e500 violates the architectural specification for these instructions because it sets the

overflow bit in cases where there is no overflow.

3

Although the e500 records any overflow resulting from the addition/subtraction portion of these instructions, a saturate value

is not saved to rD or the accumulator. The architecture specifies that the intermediate result should be saturated if it cannot

be represented in 64 bits. The also architecture specifies that the final result should be saturated if it cannot be represented

in 64 bits. The e500 does not saturate in either case.

Table 3-36. SPE APU Vector Instructions (continued)

Instruction Mnemonic Syntax

Loading...

Loading...