PowerPC e500 Core Family Reference Manual, Rev. 1

12-14 Freescale Semiconductor

Memory Management Units

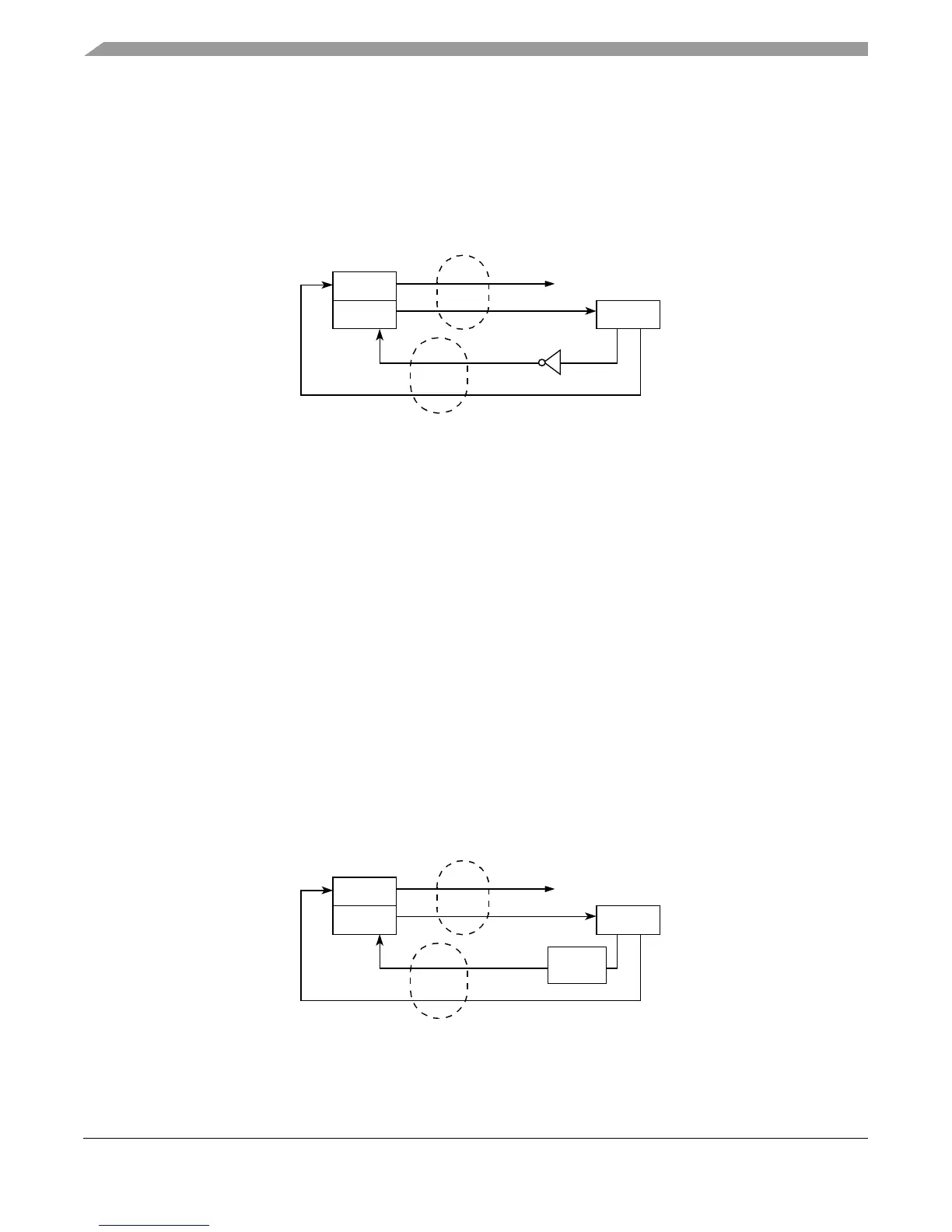

12.3.2.2.1 Round-Robin Replacement for TLB0—e500v1

Figure 12-8 shows the round-robin replacement algorithm for the e500v1 core. Note that for the

e500v1, TLB[NV] is implemented as a single bit that corresponds to the least significant bit of the

MAS0[NV] field.

Figure 12-8. Round Robin Replacement for TLB0—e500v1

On execution of a tlbwe instruction, MAS0[ESEL] selects the way of TLB0 to be loaded (way 0

or way 1). Also, when MAS0[TLBSEL] = 00 (selecting TLB0), TLB0[NV] is loaded with the

MAS0[NV

lsb

] value on execution of a tlbwe instruction. In addition, when a TLB miss exception

occurs (causing a TLB error interrupt), if MAS4[TLBSELD] = 00, the hardware automatically

loads the current value of TLB0[NV1] into MAS0[ESEL] and the complement of TLB0[NV] into

MAS0[NV

lsb

]. This sets up MAS0 such that if those values are not overwritten, the alternate way

will be selected on the next execution of a tlbwe instruction, effectively alternating between way

0 and way 1 for writing TLB0 entries.

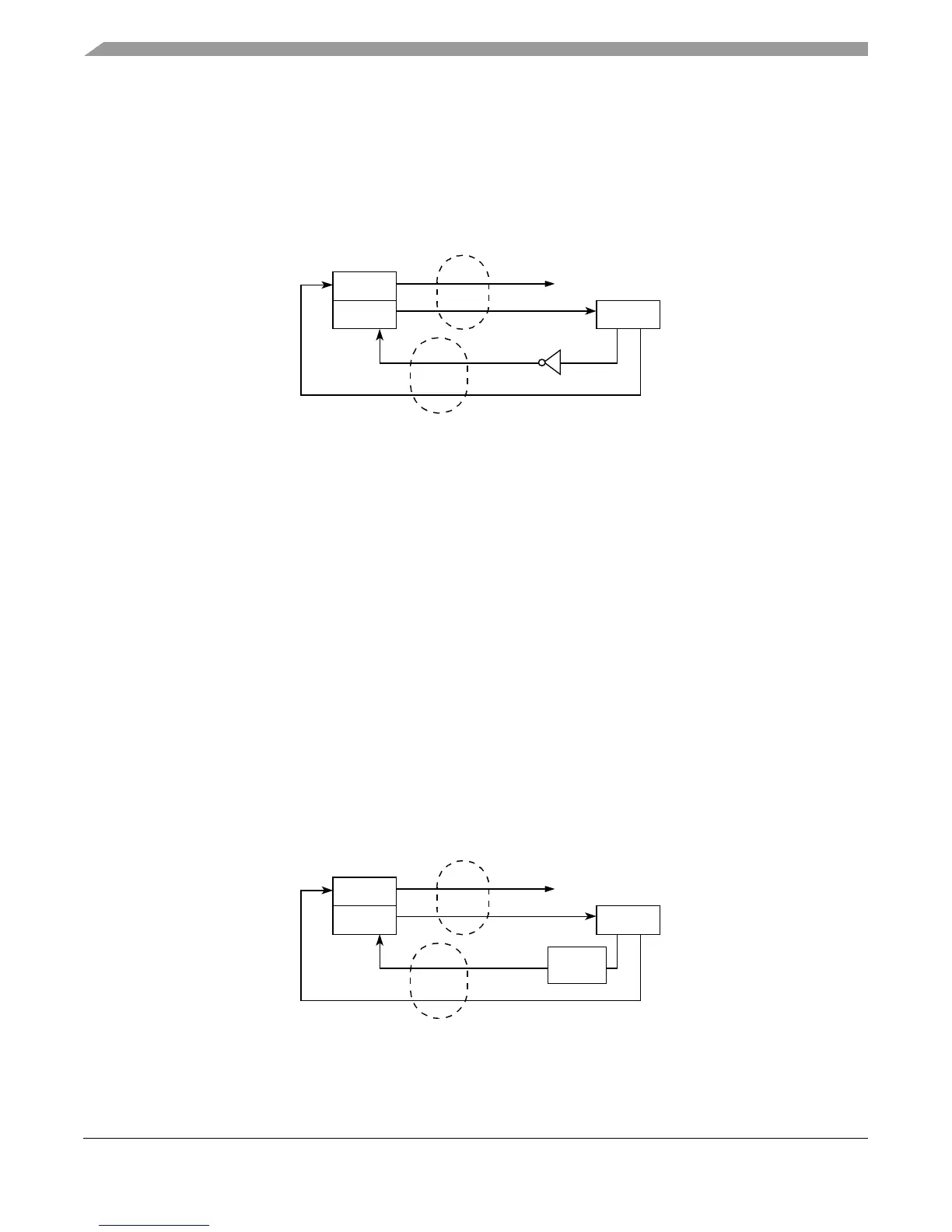

12.3.2.2.2 Round-Robin Replacement for TLB0—e500v2

The e500v2 core has a 4-way set associative TLB0, and so fully implements the round-robin

scheme with a simple 2-bit counter that increments the 2-bit value of NV from TLB0 on each TLB

miss and loads the incremented value into MAS0[NV] for use by the next tlbwe instruction.

Figure 12-9. Round Robin Replacement for TLB0—e500v2

MAS0

ESEL

NV

lsb

TLB0

NV

selects way

tlbwe (if MAS0[TLBSEL] = 00)

TLB miss (TLB error interrupt)

if MAS4[TLBSELD] = 00

MAS0

ESEL

NV

TLB0

NV

selects way

tlbwe (if MAS0[TLBSEL] = 00)

TLB miss (TLB error interrupt)

if MAS4[TLBSELD] = 00

2-bit

counter

Loading...

Loading...