Execution Timing

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 4-9

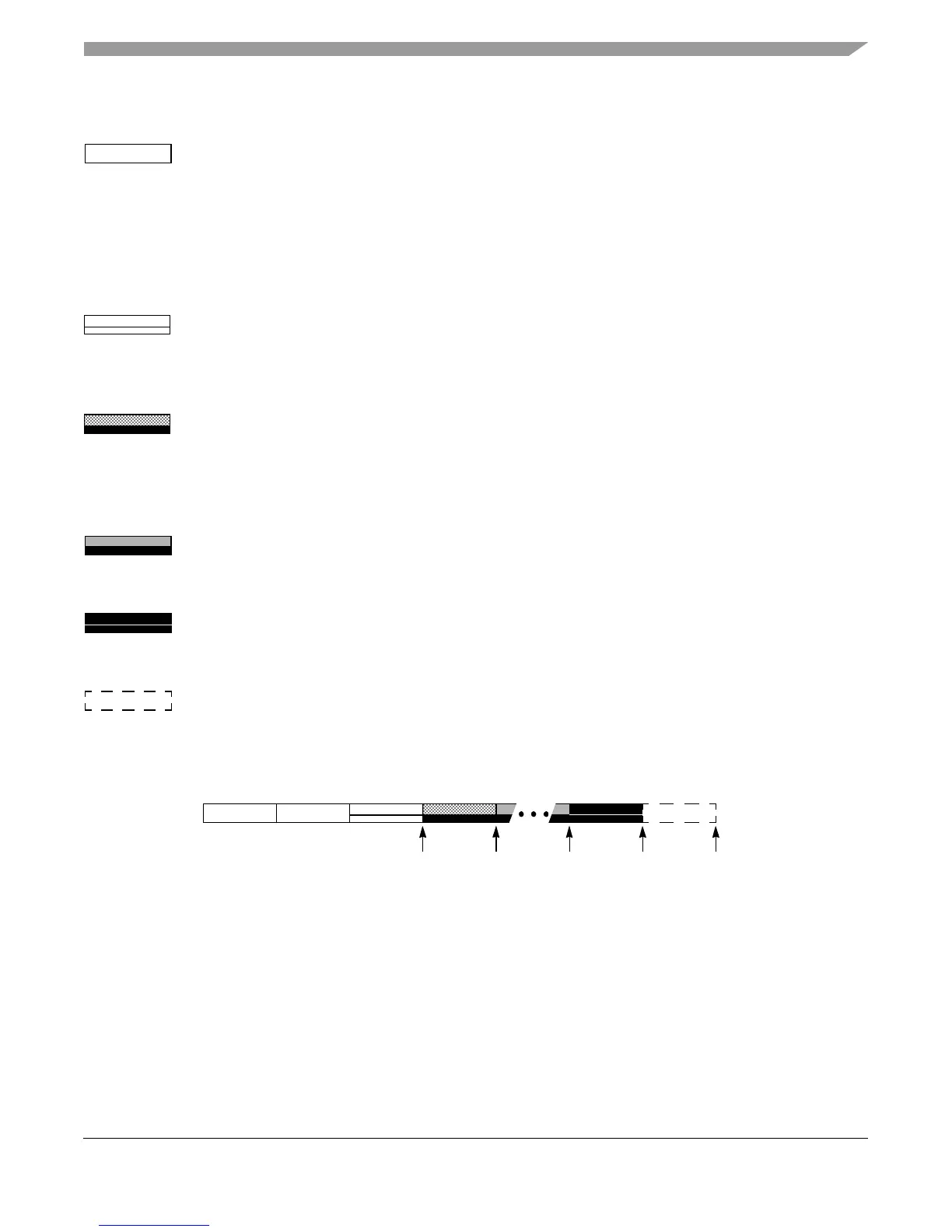

Conventions used in the instruction timing examples are as follows:

Fetch—Instructions are fetched from memory and placed in the 12-entry

IQ. The latency associated with accessing an instruction depends on

whether the instruction is in the on-chip cache or system memory (in which

case latency is further affected by bus traffic, bus clock speed, and address

translation issues). Therefore, in the examples in this chapter, the diagrams

and fetch stage shown is for the common case of instructions hitting in the

instruction cache.

Decode—As many as two eligible instructions dispatch from IQ0–IQ1 to

the appropriate issue queue. Note that isync, rfi, sc, and some other

instructions do not go to issue queues. At the same time, the instruction is

assigned an entry in the completion queue.

Issue—Instructions are dispatched to issue queues from the instruction

queue entries. At the end of the issue stage, instructions and their operands,

if available, are latched into execution unit reservation stations. The black

stripe is a reminder that the instruction occupies an entry in the CQ,

described in Figure 4-4.

Execute—The operations specified by an instruction are being performed

by the appropriate execution unit. The black stripe is a reminder that the

instruction occupies an entry in the CQ, described in Figure 4-4.

Complete—Execution has finished. When all completion requirements are

met, the instruction is retired from the CQ. The results are written back to

architecture-defined registers in the clock cycle after retirement.

Write back—The instruction has retired and its results are written back to

the architecture-defined registers.

Figure 4-4 shows the relationships between stages and events associated with them.

Figure 4-4. Execution Pipeline Stages and Events

The events are described as follows:

• Dispatch (at the end of decode)—An instruction is dispatched to the appropriate issue

queue at the end of the decode stage. At dispatch, the instruction passes to the issue pipeline

stage by taking a place in the CQ and in one of the two issue queues.

• Issue (at the end of the issue stage)—The issue stage ends when the instruction is issued to

the appropriate execution unit.

Fetch2 Decode Execute CompleteIssue

Dispatch

Issue Finish Retire

Write back

Write Back

Fetch1

Loading...

Loading...