Power Management

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 6-5

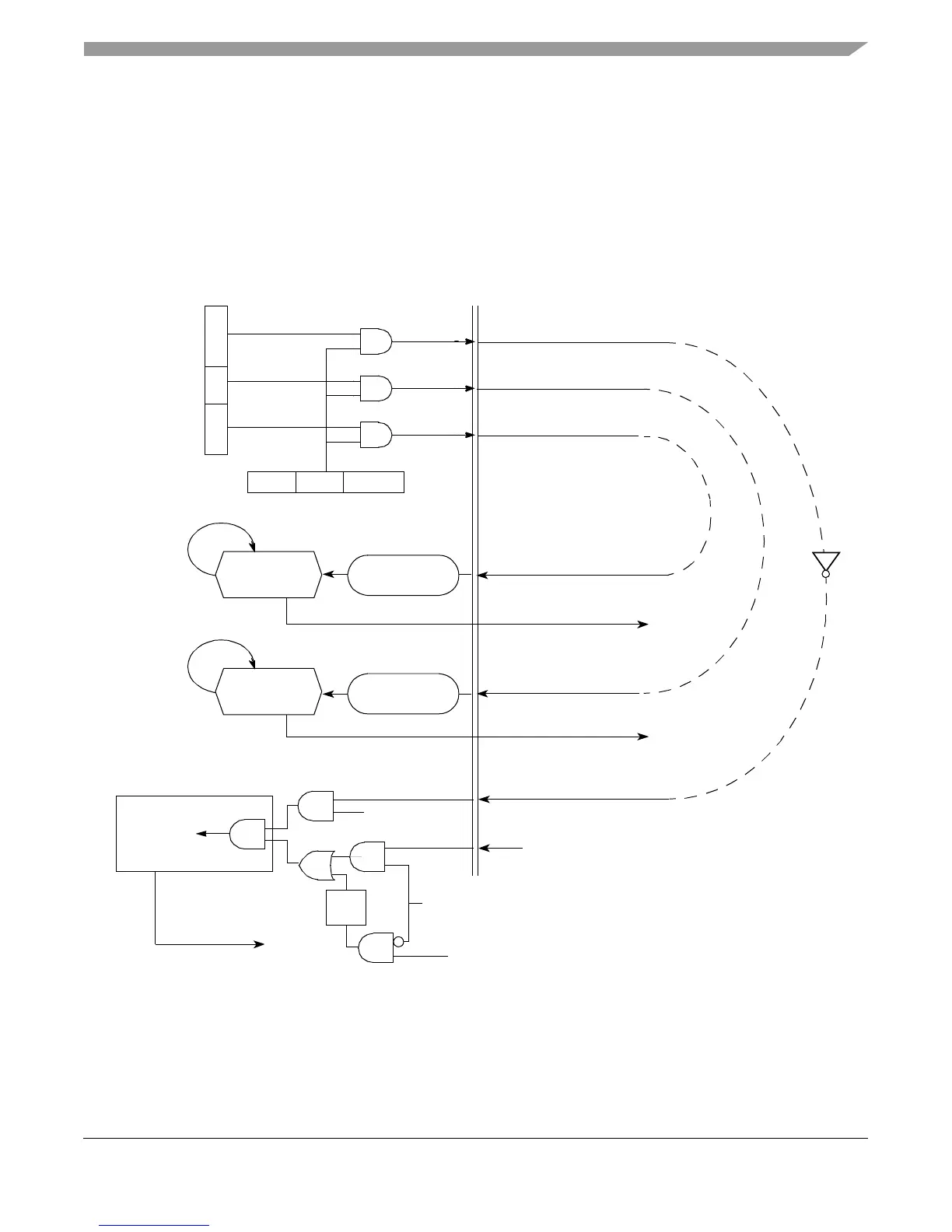

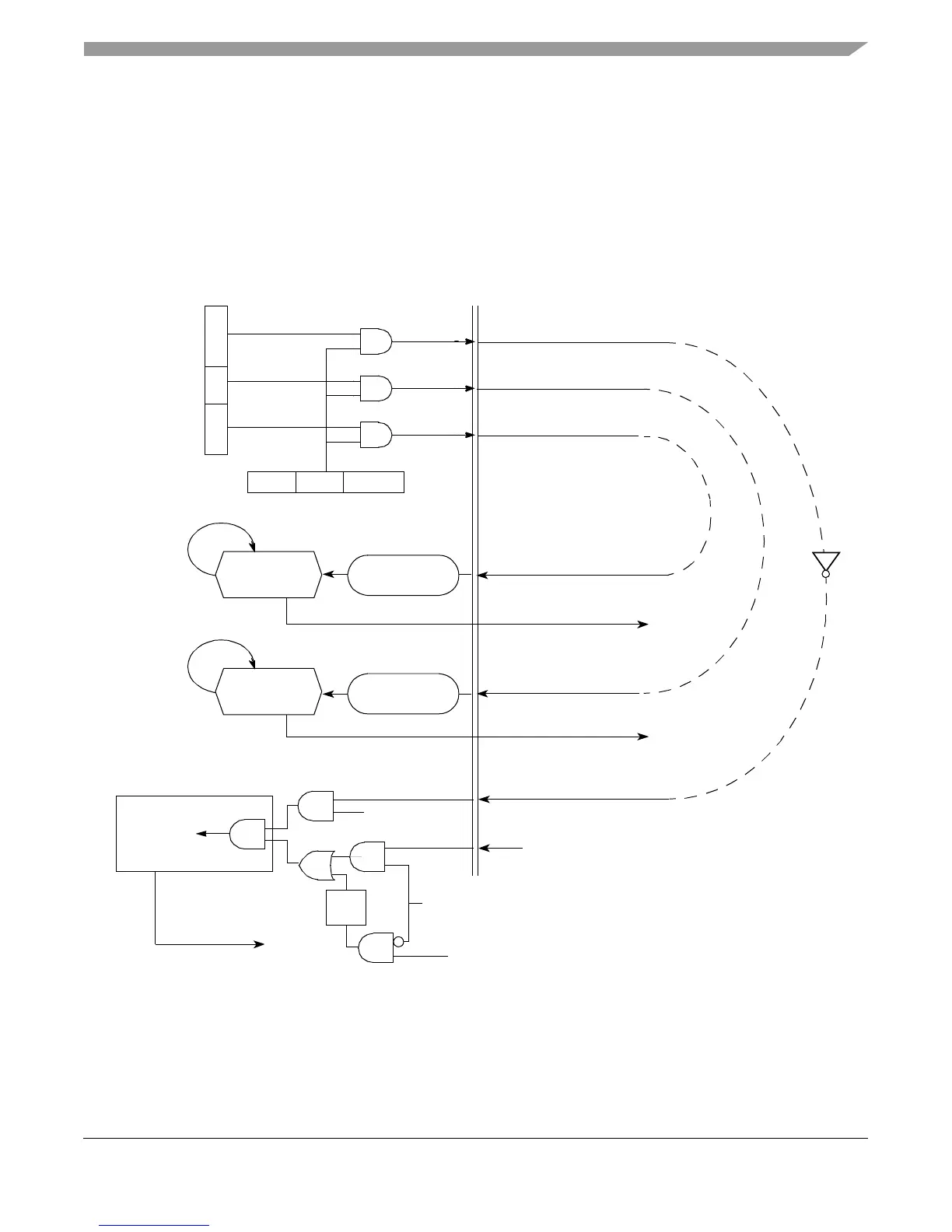

6.5 Power Management Protocol

The e500 outputs the doze, nap, and sleep signals to the integrated device logic, which controls

power states both for the device as a whole and for the core (namely the core-halted and

core-stopped states). Figure 6-2 shows how device integration logic would typically respond to

doze, nap, and sleep and control the core’s power state through the halt/halted, stop/stopped, and

tben/tbint signal pairs.

Figure 6-2. Example Core Power Management Handshaking

MSR

WE

HID0

NAPDOZE SLEEP

sleep

nap

doze

Core Complex Device Integration Logic

halted

stop

halt

tben

Stop Fetching

Instructions

Instruction

Execution

Stopped?

Ye s

No

stopped

Stop Clock

Distribution

Clock

Distribution

Stopped?

Ye s

No

(negating

tben

disables the time base.)

HID0[SEL_TBCLK]

8

÷

CCB Clock

tbint

Core Timer Facilities

Core Timer

Clock

(Time Base)

HID0[TBEN]

System clock

Loading...

Loading...