PowerPC e500 Core Family Reference Manual, Rev. 1

3-18 Freescale Semiconductor

Instruction Model

The following sequence synchronizes the instruction stream (using either dcbst or dcbf):

dcbst (or dcbf) |update memory

msync |wait for update

icbi |remove (invalidate) copy in instruction cache

msync |ensure the ICBI invalidate is complete

isync |remove copy in own instruction buffer

These operations are required because the data cache is a write-back cache. Because instruction

fetching bypasses the data cache, changes to items in the data cache cannot be reflected in memory

until the fetch operations complete. The msync after the icbi is required to ensure that the icbi

invalidation has completed in the instruction cache.

Special care must be taken to avoid coherency paradoxes in systems that implement unified

secondary caches (like the e500), and designers should carefully follow the guidelines for

maintaining cache coherency discussed in Chapter 11, “L1 Caches.”

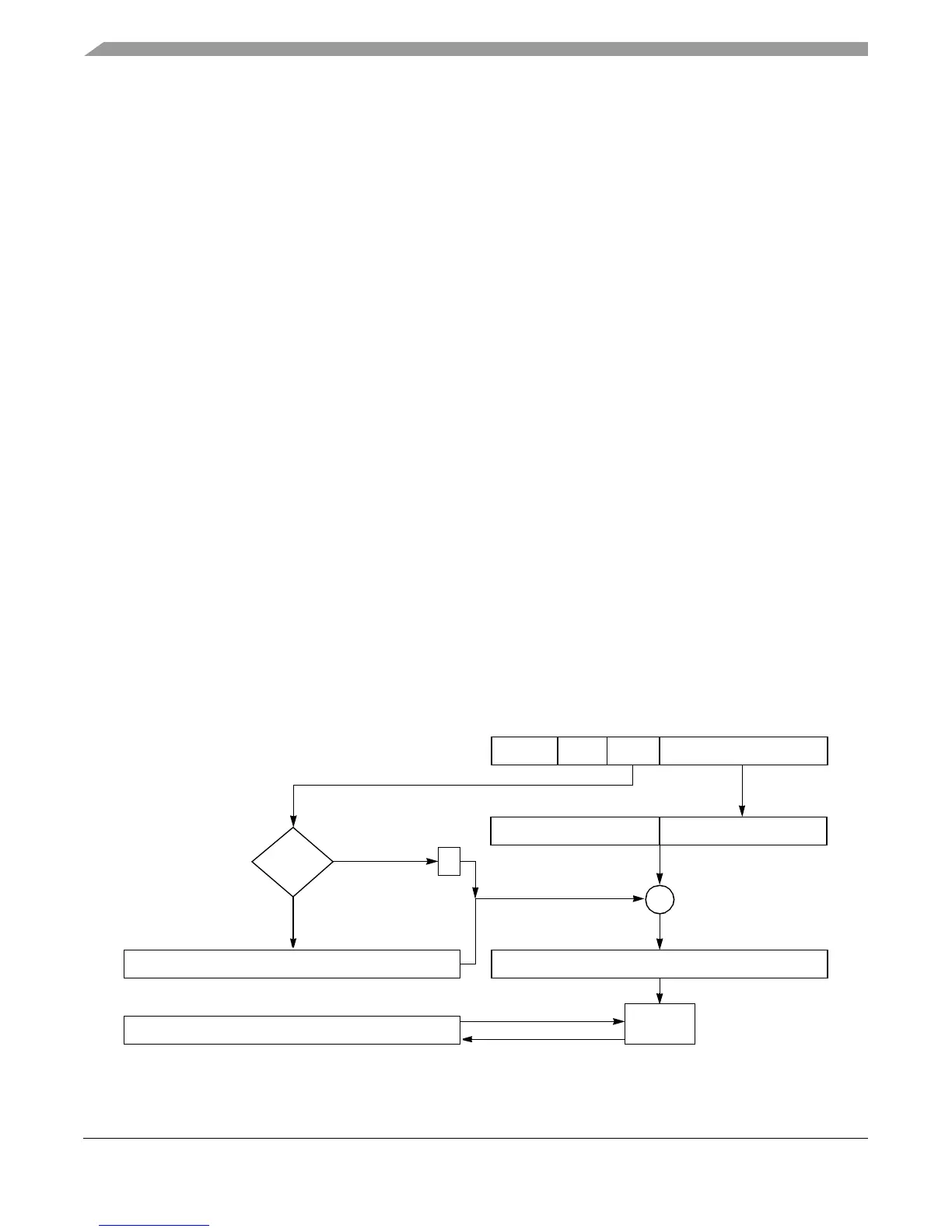

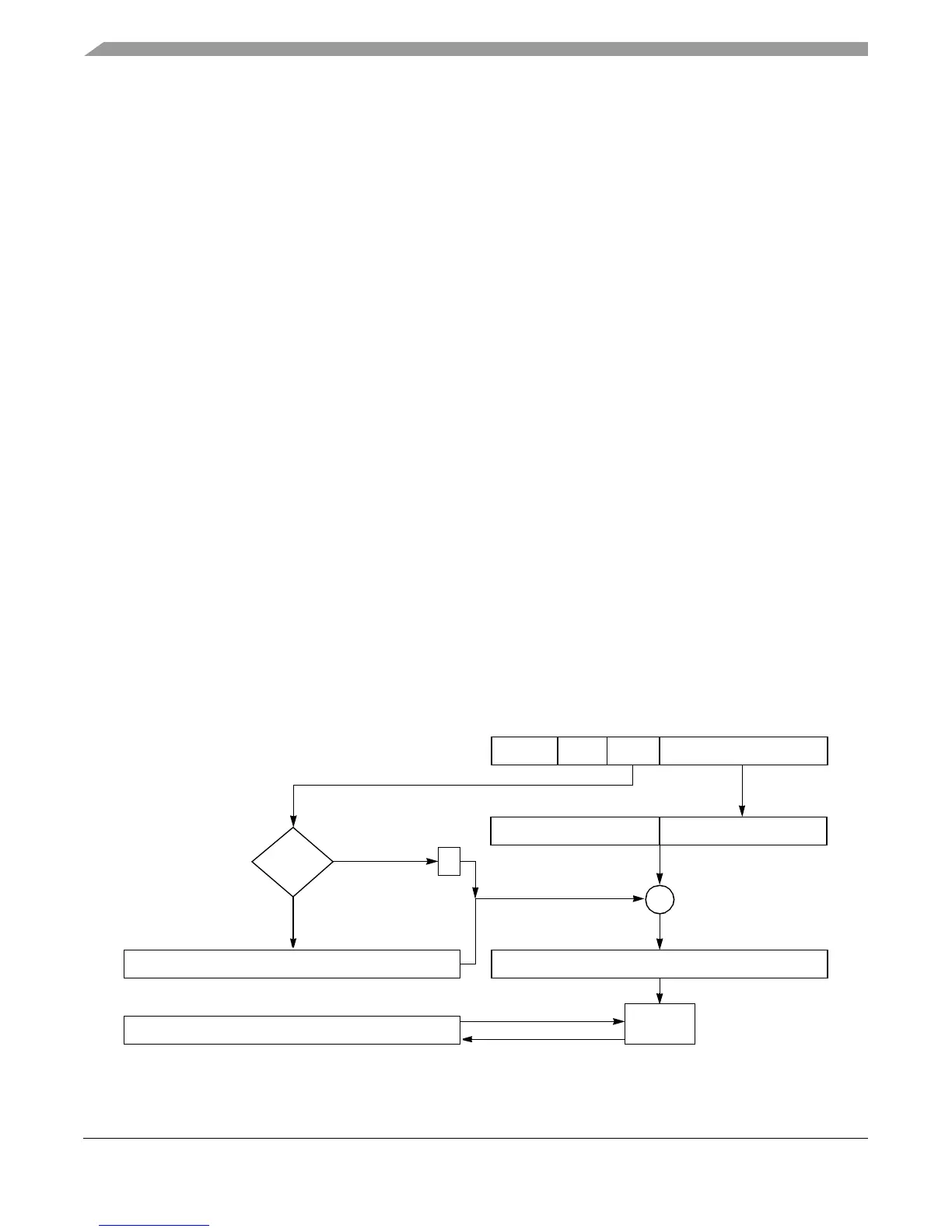

3.3.1.2.2 Integer Load and Store Address Generation

Integer load and store operations generate effective addresses using register indirect with

immediate index mode, register indirect with index mode, or register indirect mode, which are

described as follows:

• Register indirect with immediate index addressing for integer loads and stores. Instructions

using this addressing mode contain a signed 16-bit immediate index (d operand), which is

sign extended and added to the contents of a general-purpose register specified in the

instruction (rA operand), to generate the effective address. If the rA field of the instruction

specifies r0, a value of zero is added to the immediate index (d operand) in place of the

contents of r0. The option to specify rA or 0 is shown in the instruction descriptions as

(rA|0). Figure 3-1 shows how an effective address is generated using this addressing mode.

Figure 3-1. Register Indirect with Immediate Index Addressing for Integer Loads/Stores

No

0 15 16 31

Sign Extension d

32 63

GPR (rA)

0

32 63

GPR (rD/rS)

Store

Load

Ye s

Instruction Encoding:

05610111516 31

Opcode rD/rS rAd

+

031

Effective Address

rA=0?

Memory

Interface

Loading...

Loading...