Instruction Model

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 3-61

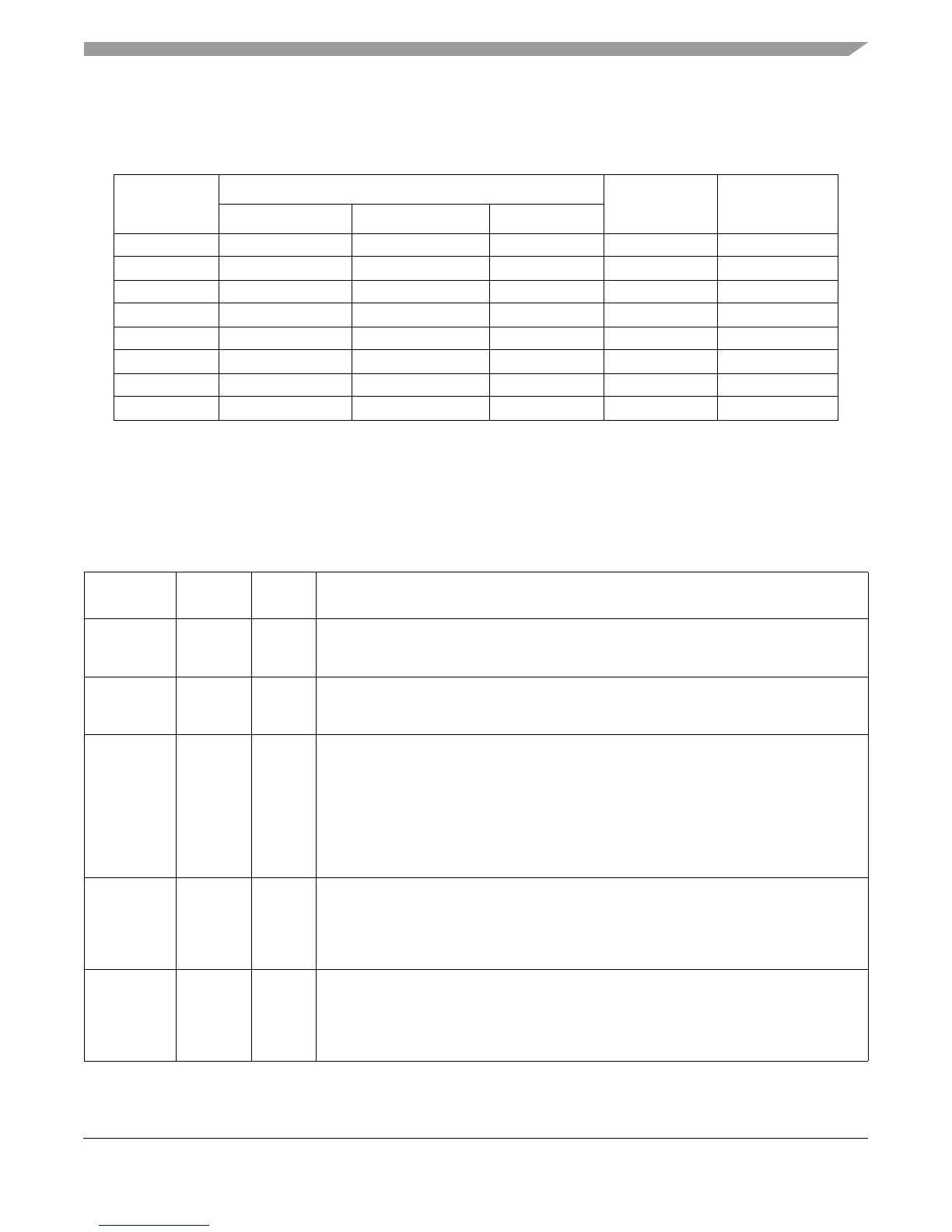

PMR encodings are shown in Table 3-40.

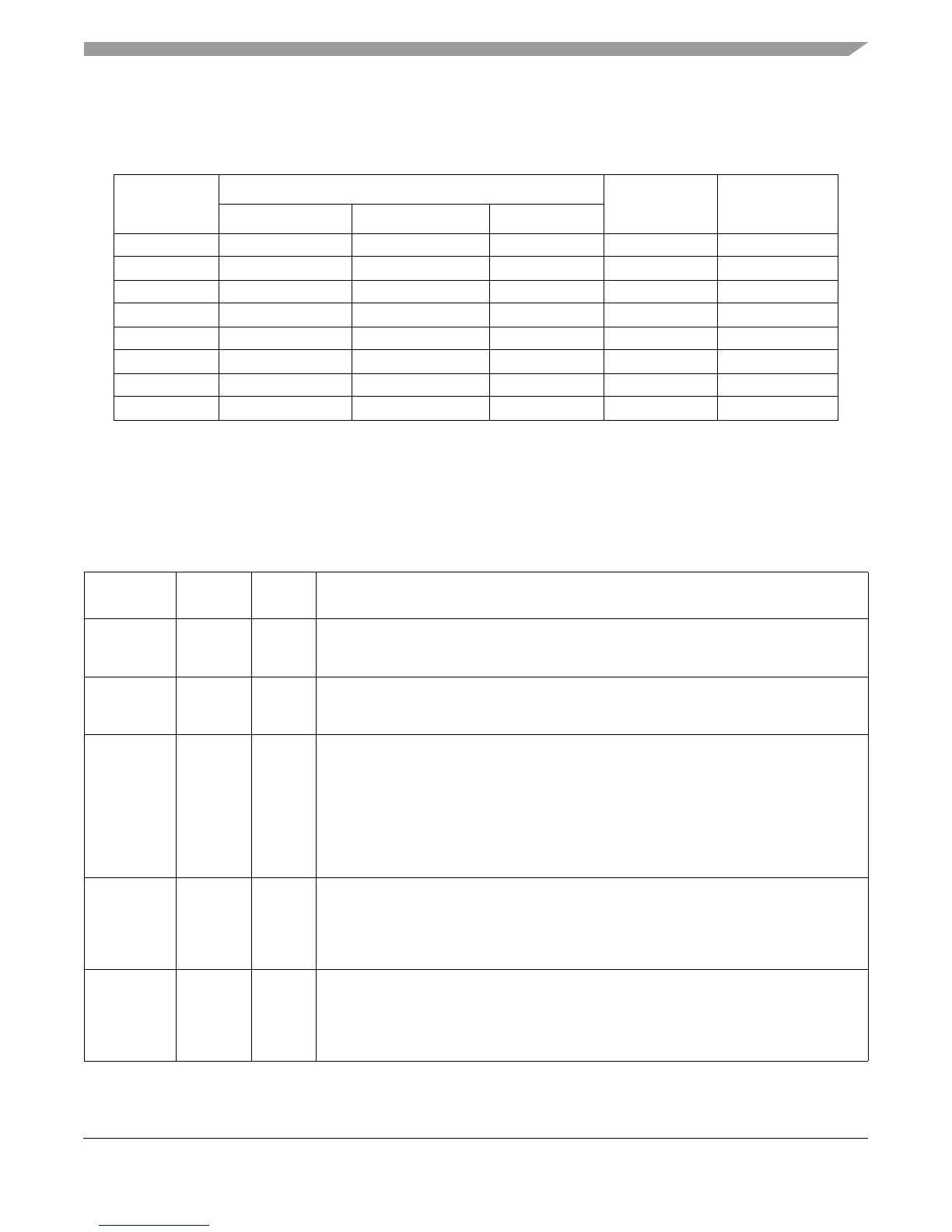

3.8.4 Cache Locking APU

This section describes the instructions in the cache locking APU, which consists of the instructions

described in Table 3-41.

Table 3-40. e500-Defined PMR Encodings

Register Name

PMR

Privilege Access

Decimal pmr[5–9] pmr[0–4]

UMMCR0 936 11101 01000 User Read only

UMMCR1 940 11101 01100 User Read only

UMMCR2 928 11101 00111 User Read only

UPMC1 937 11101 01001 User Read only

UPMC2 938 11101 01010 User Read only

UPMC3 941 11101 01101 User Read only

UPMC4 942 11101 01110 User Read only

USIAR 939 11101 01011 User Read only

Table 3-41. Cache Locking APU Instructions

Name

Mnemoni

c

Syntax Implementation Details

Data Cache

Block Lock

Clear

dcblc CT,rA,rB If CT=0 and the line is in the L1 data cache, the data cache lock bit for that line is cleared,

making it eligible for replacement. If CT=1 and the line is in the L2 cache, the lock bit for

that line is cleared, making it eligible for replacement.

Data Cache

Block Touch

and Lock Set

dcbtls CT,rA,rB If CT=0, the line is loaded and locked into the L1 data cache. If CT=1, the line is loaded

and locked in the unified L2 cache. If CT=1 and the block is already in the L2 cache, dcbtls

marks the block so it is not a candidate for replacement.

Data Cache

Block Touch

for Store and

Lock Set

dcbtstls CT,rA,rB If CT = 0, the e500 core fetches the block containing the byte addressed by EA into the

data cache. After the block containing the byte is fetched, it is locked. If CT = 0 and the

block is in the data cache, dcbtstls marks the block locked so it is no longer eligible for

replacement.

If CT=1 and the block is in the L2 cache, dcbtstls marks the block such that it should not

be selected for replacement.

If CT is not 0 or 1, dcbtstls is no-oped. In the L1 data cache, the e500 implements a lock

bit for every index and way, allowing a line locking granularity.

Instruction

Cache Block

Lock Clear

icblc CT,rA,rB If CT=0 and the line is in the instruction cache, the lock bit for that line is cleared, making

it eligible for replacement.

If CT=1 and the line is in the L2 cache, the lock bit for that line is cleared in the L2 cache,

making it eligible for replacement.

If CT is not 0 or 1, the icblc is no-oped.

Instruction

Cache Block

Touch and

Lock Set

icbtls CT,rA,rB If CT=0, the line is loaded and locked into the L1 instruction cache. If CT=1, the line is

loaded into the unified L2 cache and the line is locked into the L2 cache.

If CT=1 and the block already exists in the L2 cache, icbtls marks it such that it should not

be selected for replacement.

If CT is not 0 or 1, icbtls is no-oped.

Loading...

Loading...