Instruction Model

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 3-9

Table 3-5 below identifies the software synchronization requirements for instruction fetch and/or

execution for all context-altering instructions.

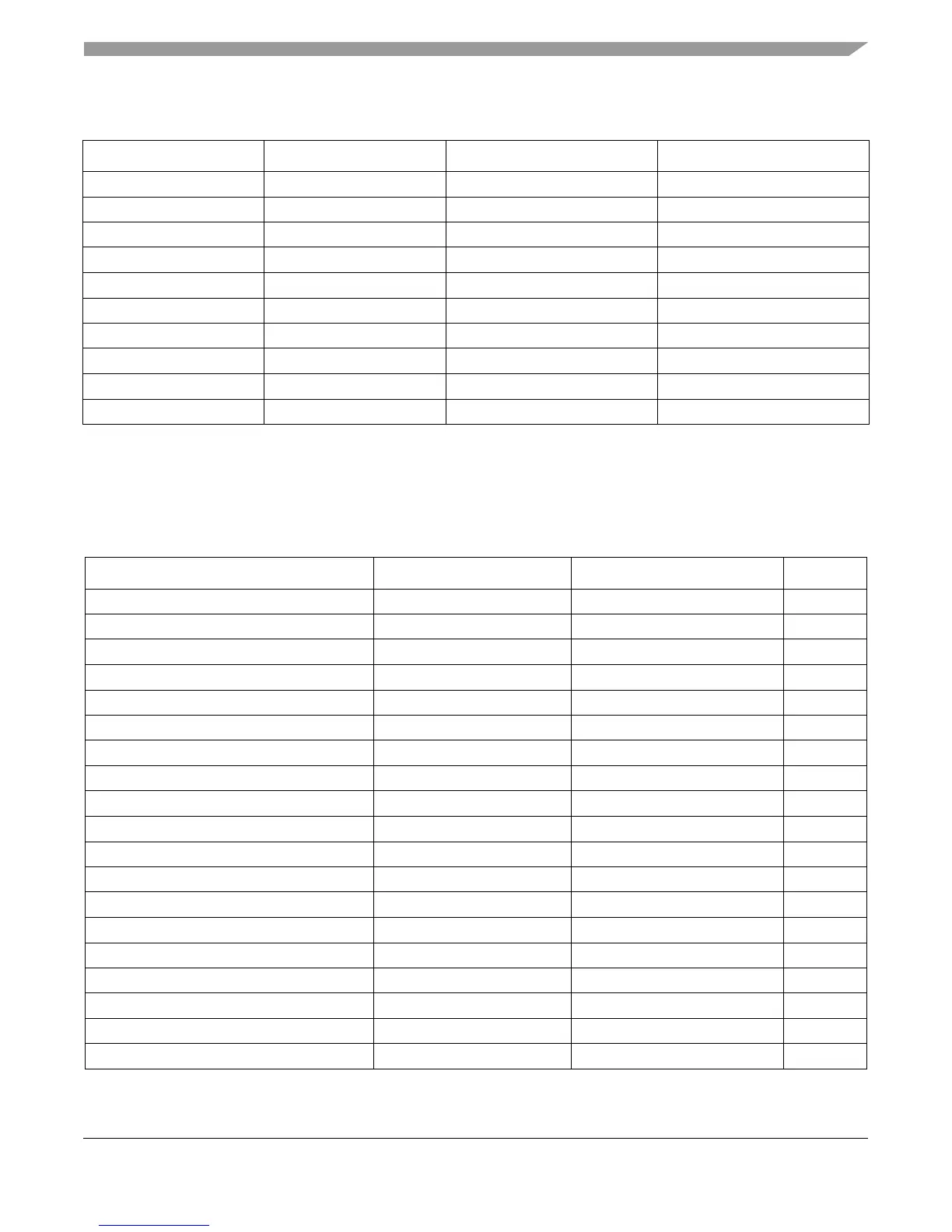

BUCSR mtspr bucsr None CSI

1

DBCR0 mtspr dbcr0 None CSI

1

DBCR1 mtspr dbcr1 None CSI

1

HID0 mtspr hid0 CSI

1

CSI

1

HID1 mtspr hid1 msync CSI

1

L1CSR0 mtspr l1csr0 msync, isync CSI

1

L1CSR1 mtspr l1csr1 None isync

MMUCSR0 mtspr mmucsr0 CSI

1

CSI

1

PID0–PID2 mtspr pid[0–2] None isync

SPEFSCR mtspr spefscr None isync

1

CSI indicates any context-synchronizing instruction (that is, sc, isync, rfci, or rfi).

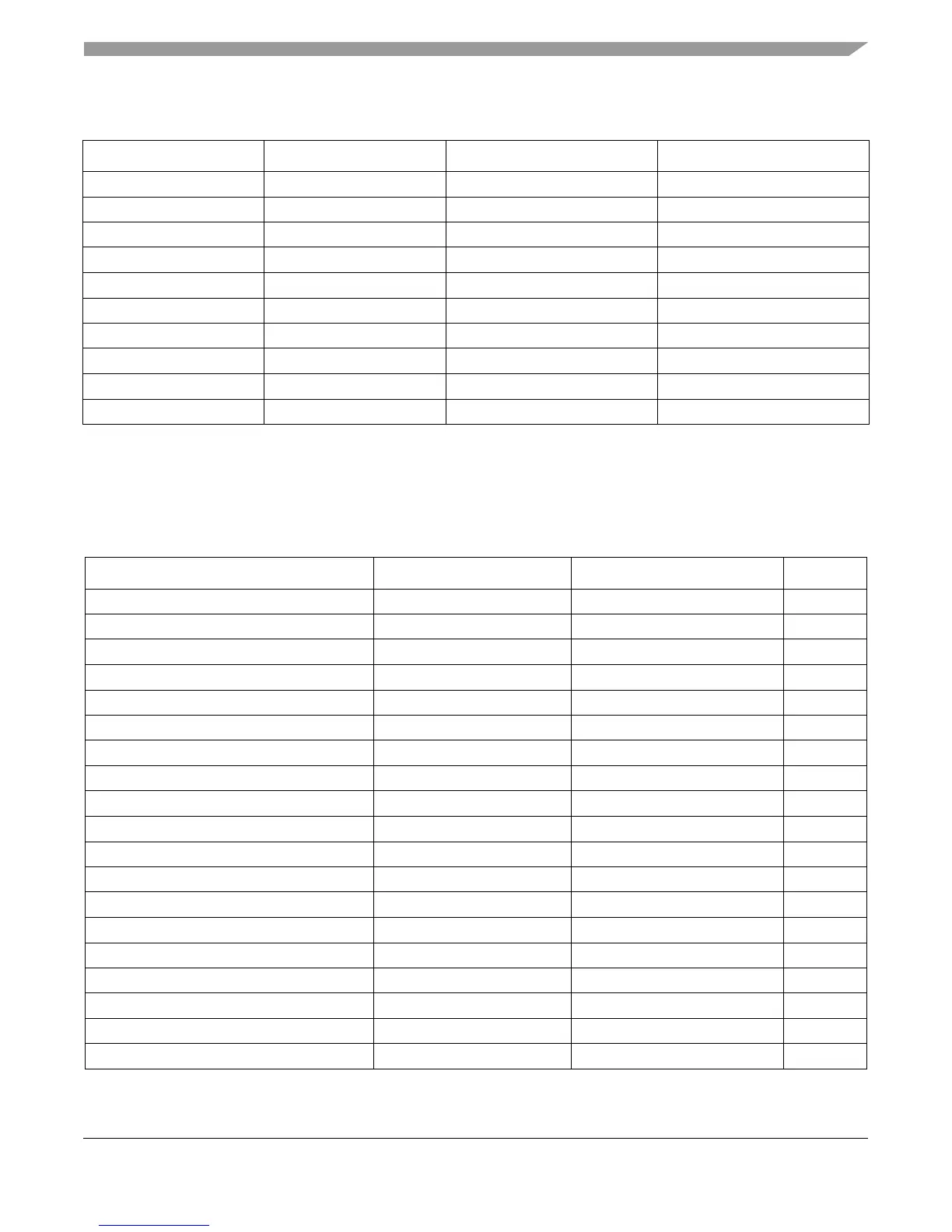

Table 3-5. Instruction Fetch and/or Execution Synchronization Requirements

Context Altering Instruction or Event Required Before Required After Notes

Interrupt None None

mtmsr (CE) None None

1

mtmsr (DE) None CSI

4

mtmsr (EE) None None

1

mtmsr (FE0) None CSI

4

mtmsr (FE1) None CSI

4

mtmsr (FP) None CSI

4

mtmsr (IS) None CSI

42

mtmsr (ME) None CSI

45,3

mtmsr (PR) None CSI

4

mtmsr (WE) The e500 requires an msync. The e500 requires an isync.

5,6

mtpmr None CSI

7

mtspr (DAC

n

)—CSI

8

mtspr (DBCR

n

)—CSI

8

mtspr (DBSR) — CSI

8

mtspr (DEC) None None

9

mtspr (IAC

n

)—CSI

8

mtspr (IVOR

n

) None None

mtspr (IVPR) None None

Table 3-4. Synchronization Requirements for e500-Specific SPRs (continued)

Registers Instruction Instruction Required Before Instruction Required After

Loading...

Loading...