PowerPC e500 Core Family Reference Manual, Rev. 1

4-32 Freescale Semiconductor

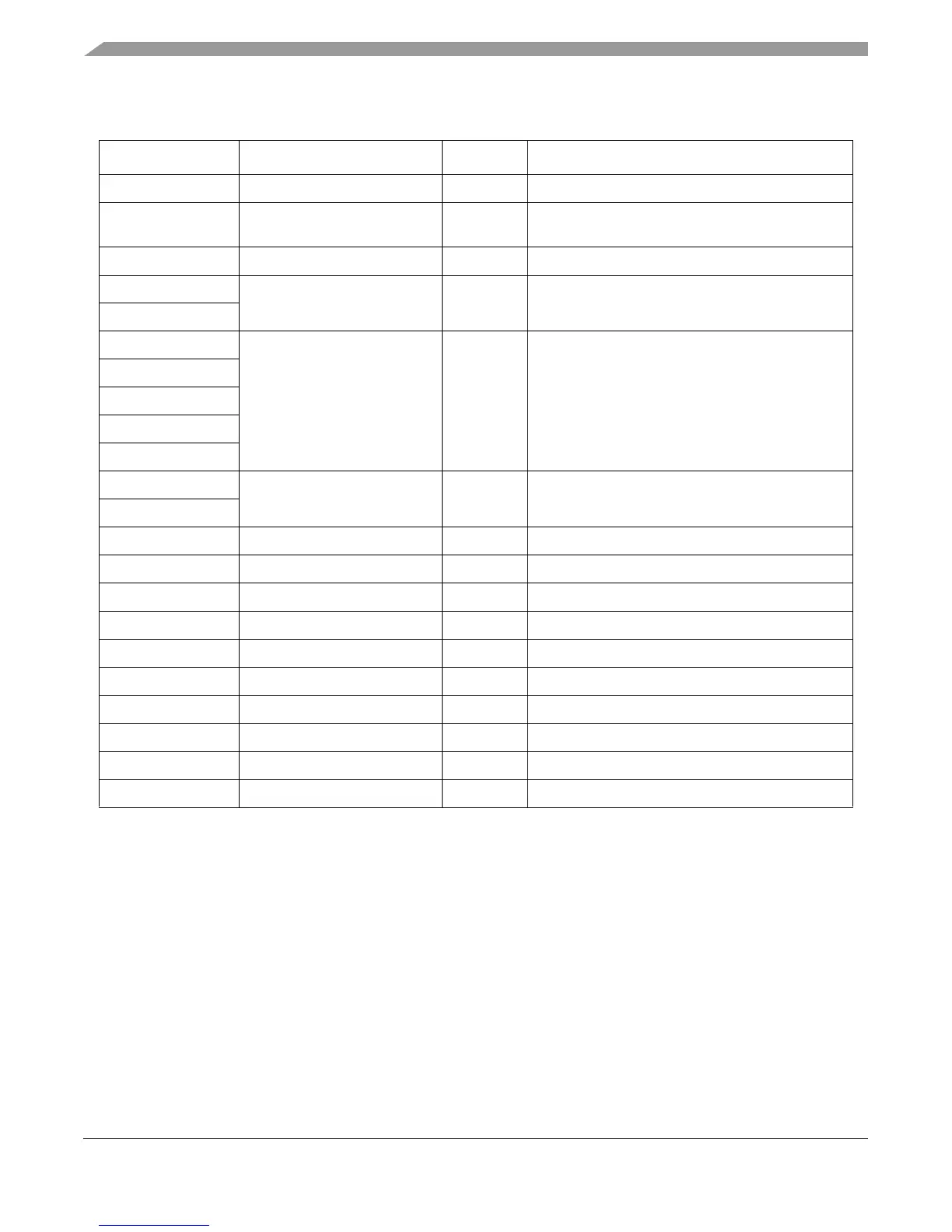

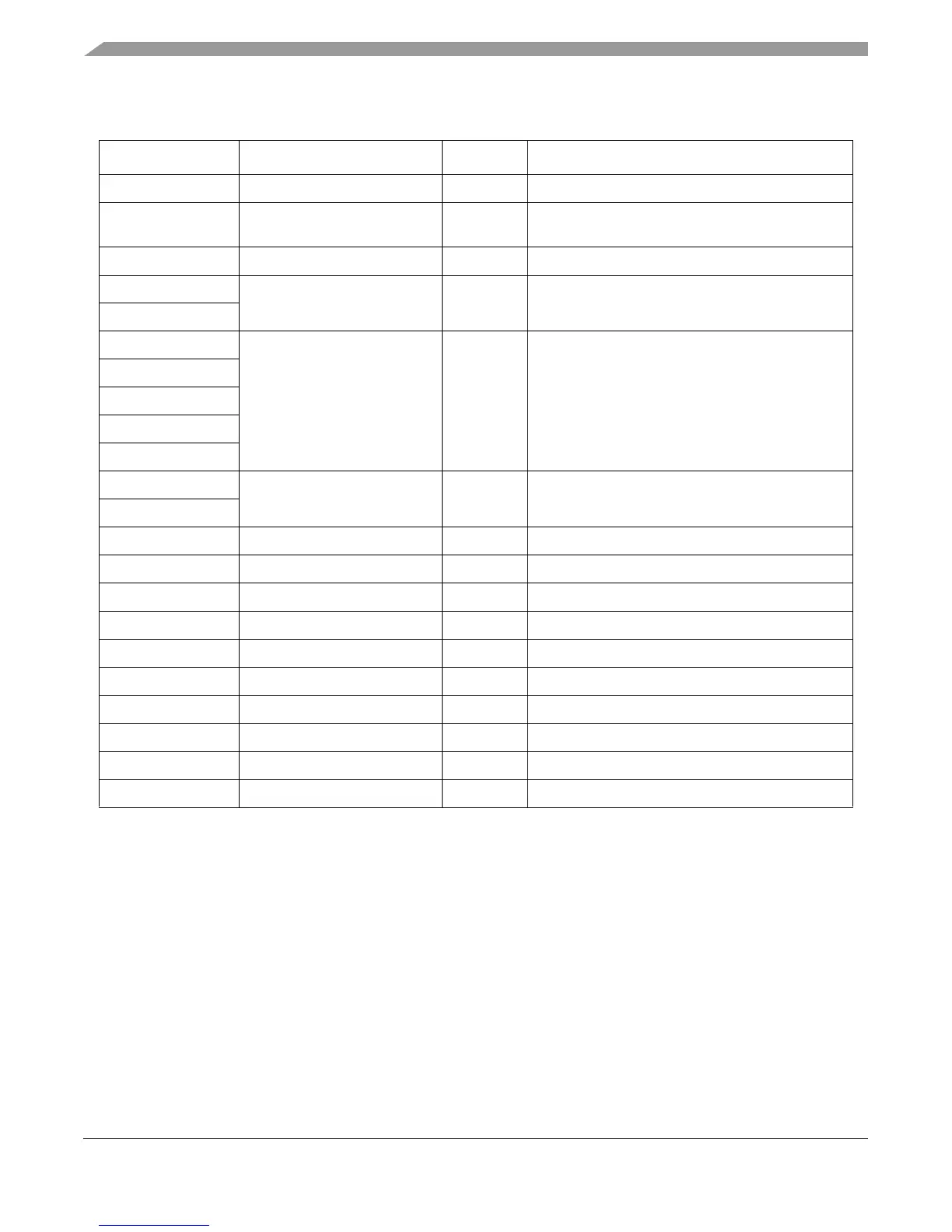

Execution Timing

mfspr (all others

6

) None SU1 only 4

7

mtcrf (single field) None SU1 or SU2 1 (one instruction per execution unit per clock cycle

throughput)

mtpmr Move-to SU1 1

mtspr[CTR]

8

Move-to SU1 only 1

mtspr[LR]

9

mtcrf (multiple field) Move-to, presync, postsync SU1 only 1

mtmsr

mtspr[CSRR0]

mtspr[DBCR0]

mtspr[DBSR]

mtspr[SSCR] Move-to, postsync SU1 only 1

mtspr[XER]

mtspr[PID

n

] Move-to, presync SU1 only 1

mtspr (all others) Move-to SU1 only 1 (one instruction per clock cycle throughput)

msync Store and postsync serialized LSU Latency depends on bus response time

rfi Refetch —

1

0

rfci Refetch —

1

0

rfmci Refetch —

1

0

sc Refetch —

1

0

tlbsync Store LSU 3 (1instruction per 18 cycle throughput)

wrtee Postsync, move-to SU1 1

wrteei Postsync, move-to SU1 1

1

Section 4.3.3.3, “Instruction Serialization,” describes the different types of serializations listed here.

2

Refetch serialized instructions (if marked with a 0-cycle execution time) do not have an execute stage, and all refetch

serialized instructions have 1 cycle between the time they are completed and the time the target/sequential instruction

enters the fetch1 stage.

3

Decode out of IQ0 only

4

mfctr stalls in decode until any outstanding mtctr finishes

5

mflr stalls in decode until any outstanding mtlr finishes

6

Includes BBTAR, BBEAR, MSR, CSRR

n

, L1CFG

n

, DAC

n

, DBCR

n

, DEAR, DEC, DECAR, ESR, IVPR, IAC

n

, IVOR

n

,

MAS

n

, PID

n

, TLBCFG

n

, HID

n

, L1CSR

n

, MMUSCR0, BUCSR, MMUCFG, PIR, PVR, SPRG

n

, SVR, MCSR, MCSRR

n

,

SRR

n

, TBL (read and write), TBU (read and write), TCR, TSR, USPRG0,

7

This instruction take 4 cycles to execute in the single-stage SU1. It occupies SU1 for all 4 cycles, so subsequent

instructions cannot enter SU1 until this instruction finishes.

8

mtctr stalls in decode until any other outstanding mtctr finishes.Throughput of 1 per 4 cycles for mtctr followed by mtctr.

9

mtlr stalls in decode until any other outstanding mtlr finishes. Throughput of 1 per 4 cycles for mtlr followed by mtlr.

Table 4-4. System Operation Instruction Execution Latencies (continued)

Mnemonic Serialization

1

Unit Cycles

Loading...

Loading...