Execution Timing

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 4-33

Table 4-5 lists condition register logical instruction latencies.

Table 4-6 lists integer instruction latencies.

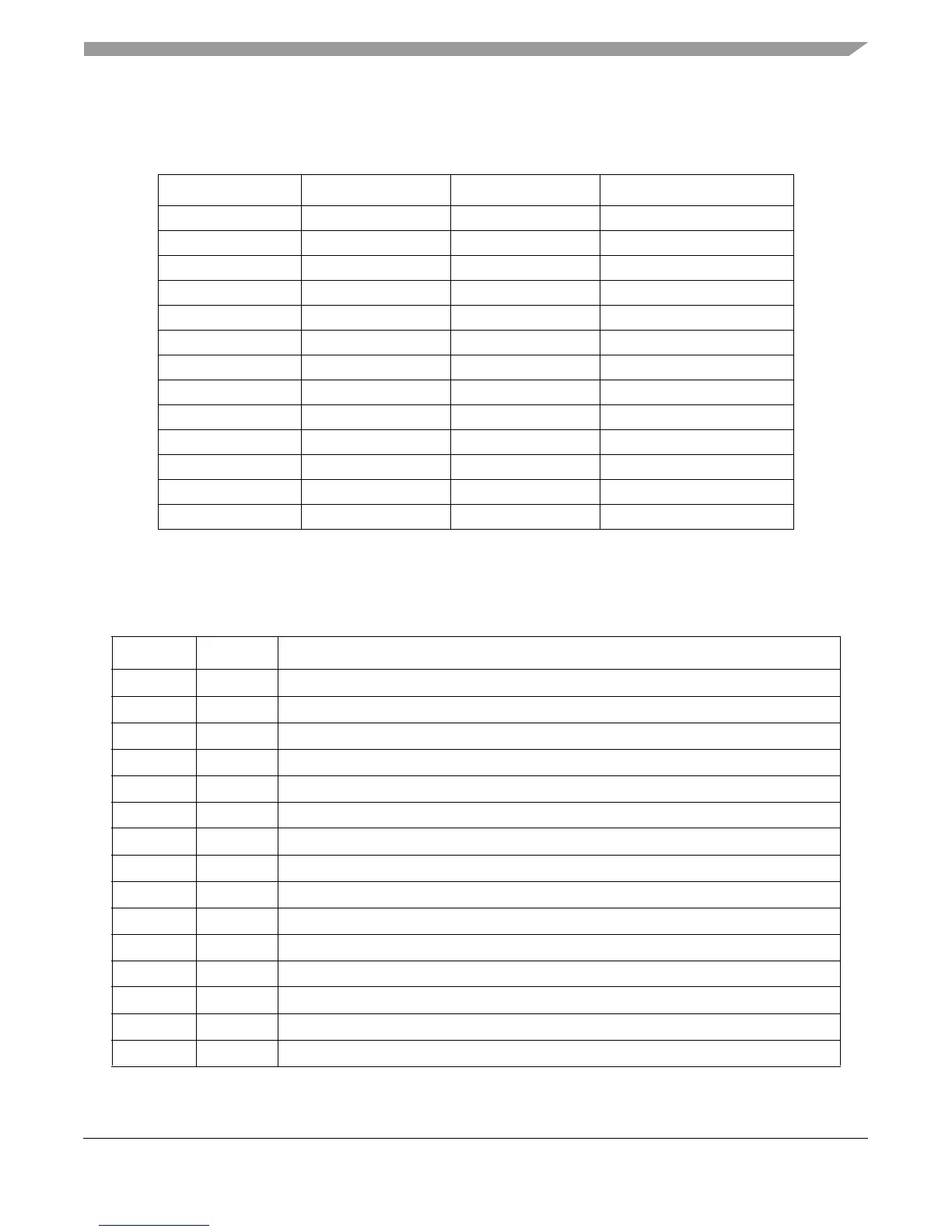

Table 4-5. Condition Register Logical Execution Latencies

Mnemonic Unit Cycles Serialization

1

1

Section 4.3.3.3, “Instruction Serialization,” describes the different types of serializations listed here.

crand BU 1 —

crandc BU 1 —

creqv BU 1 —

crnand BU 1 —

crnor BU 1 —

cror BU 1 —

crorc BU 1 —

crxor BU 1 —

mcrf BU 1 —

mcrxr BU 1 Presync, postsync

mfcr SU1 1 Move-from

mtcrf (single field) SU1 1 —

mtcrf (multiple fields) BU 2 Move-to, presync, postsync

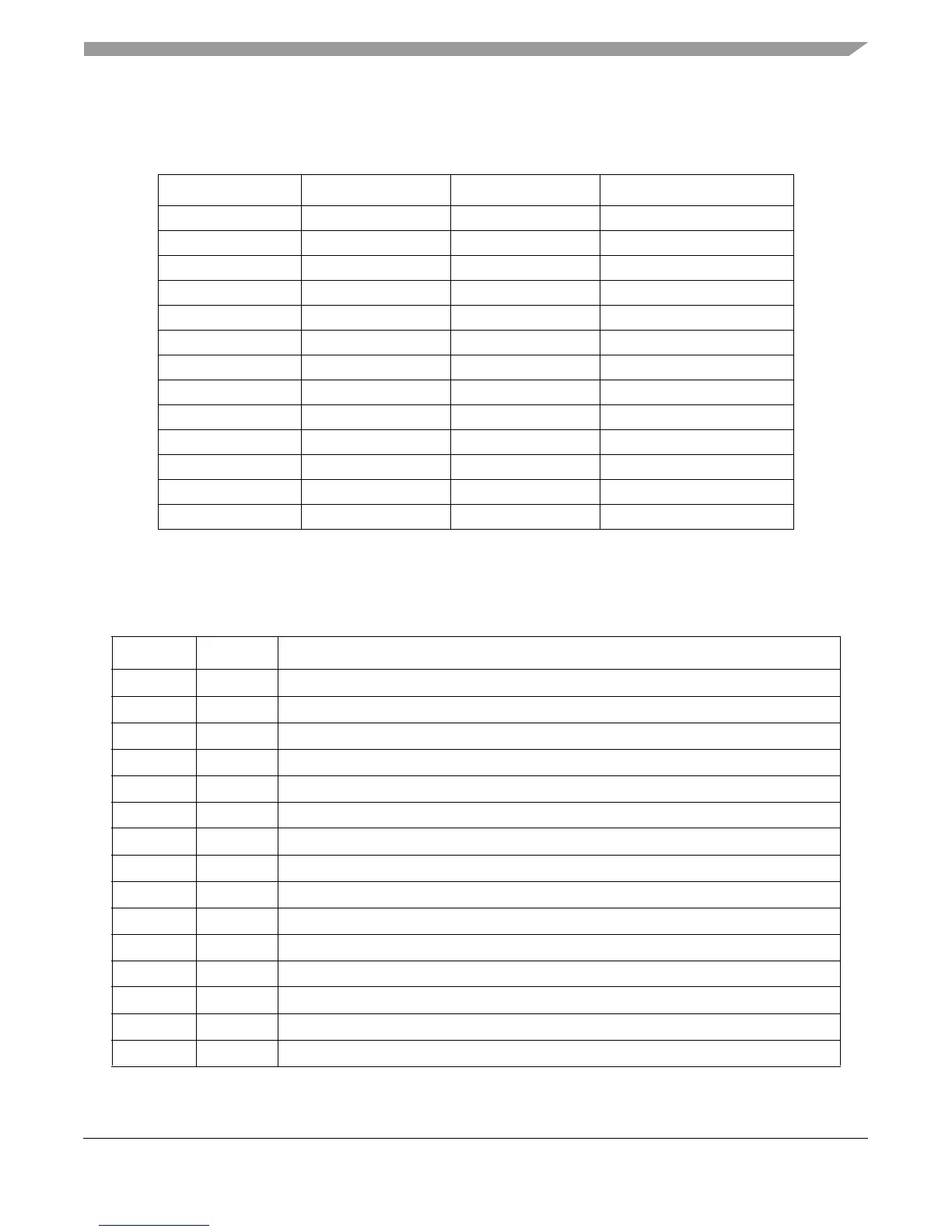

Table 4-6. SU and MU PowerPC Instruction Execution Latencies

Mnemonic Unit Cycles

addc[o][.]SU1 or SU21

1

adde[o][.]SU1 or SU21

1

addi SU1 or SU2 1

addic SU1 or SU2 1

addic. SU1 or SU2 1

1

addis SU1 or SU2 1

addme[o][.]SU1 or SU21

1

addze[o][.]SU1 or SU21

1

add[o][.]SU1 or SU21

1

andc[.]SU1 or SU21

1

andi. SU1 or SU2 1

1

andis. SU1 or SU2 1

1

and[.]SU1 or SU21

1

cmp SU1 or SU2 1

cmpi SU1 or SU2 1

Loading...

Loading...