PowerPC e500 Core Family Reference Manual, Rev. 1

4-34 Freescale Semiconductor

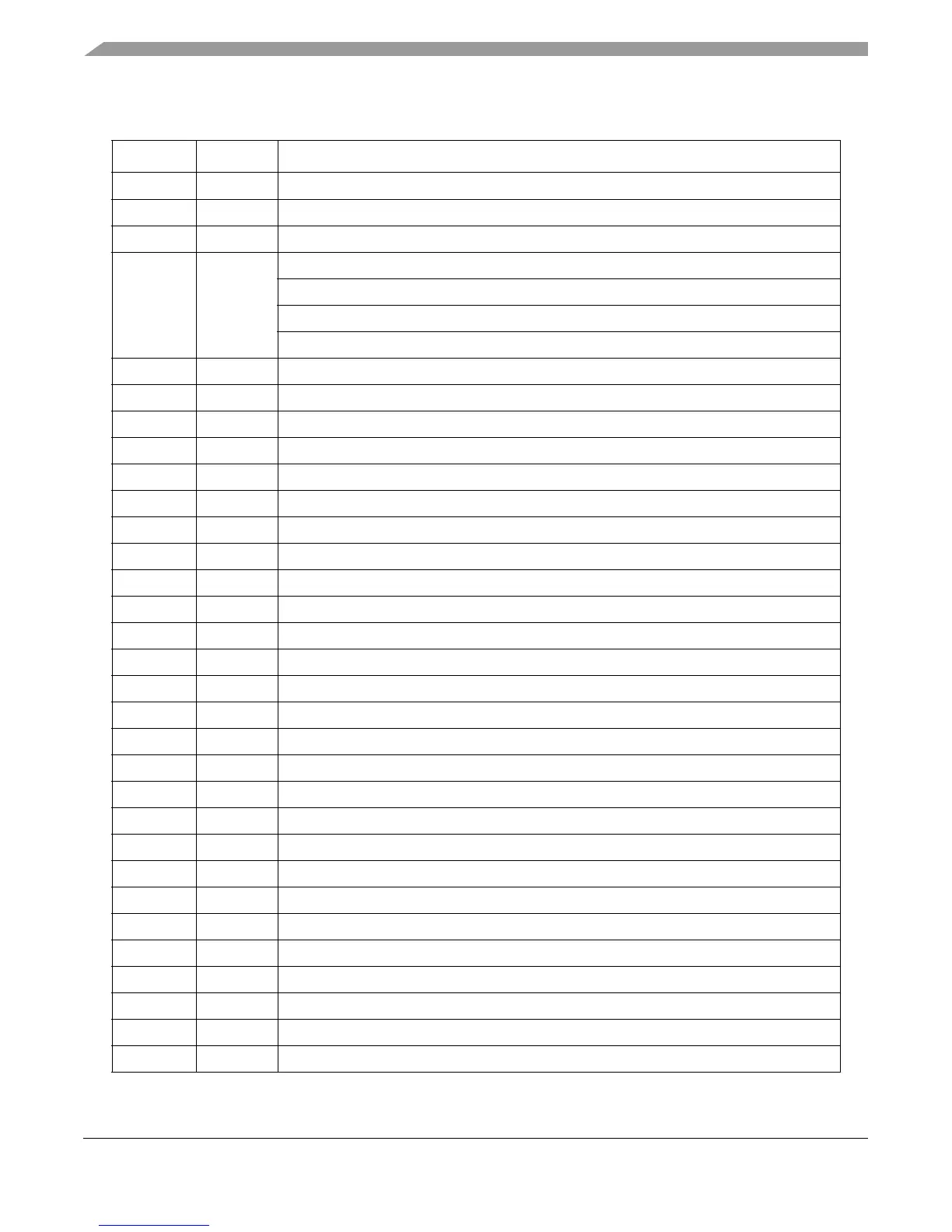

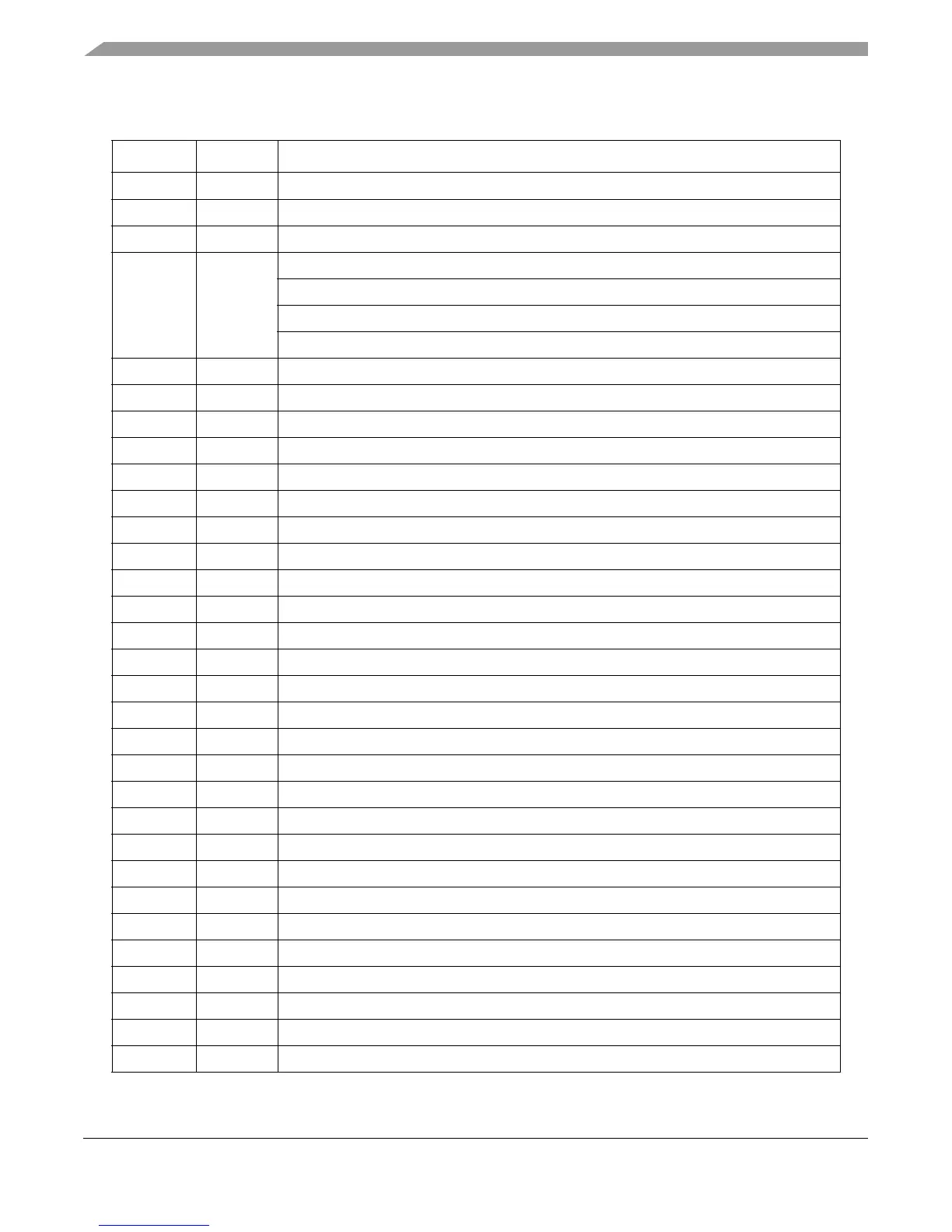

Execution Timing

cmpl SU1 or SU2 1

cmpli SU1 or SU2 1

cntlzw[.]SU11

1

divwu[o][.]

divw[o][.]

MU 4 (rA or rB = 0, minint/-1)

1,2

11 (rA can be represented as an 8-bit value within context (signed or unsigned))

1, 2

19 (rA operand can be represented as a 16-bit value within context (signed or unsigned))

1, 2

35 (all others)

1, 2

eqv[.]SU1 or SU21

1

extsb[.]SU1 or SU21

1

extsh[.]SU1 or SU21

1

isel SU1 or SU2 1

mulhwu[.]MU4:1

1, 3

mulhw[.]MU4:1

1, 3

mulli MU 4:1

3

mullw[o][.]MU4:1

1, 3

nand[.]SU1 or SU21

1

neg[o][.]SU1 or SU21

1

nor[.]SU1 or SU21

1

orc[.]SU1 or SU21

1

ori SU1 or SU2 1

oris SU1 or SU2 1

or[.]SU1 or SU21

1

rlwimi[.]SU1 or SU21

1

rlwinm[.]SU1 or SU21

1

rlwnm[.]SU1 or SU21

1

slw[.]SU1 or SU21

1

srawi[.]SU1 or SU21

1

sraw[.]SU1 or SU21

1

srw[.]SU1 or SU21

1

subfc[o][.]SU1 or SU21

1

subfe[o][.]SU1 or SU21

1

subfic SU1 or SU2 1

subfme[o][.]SU1 or SU21

1

subfze[o][.]SU1 or SU21

1

Table 4-6. SU and MU PowerPC Instruction Execution Latencies (continued)

Mnemonic Unit Cycles

Loading...

Loading...