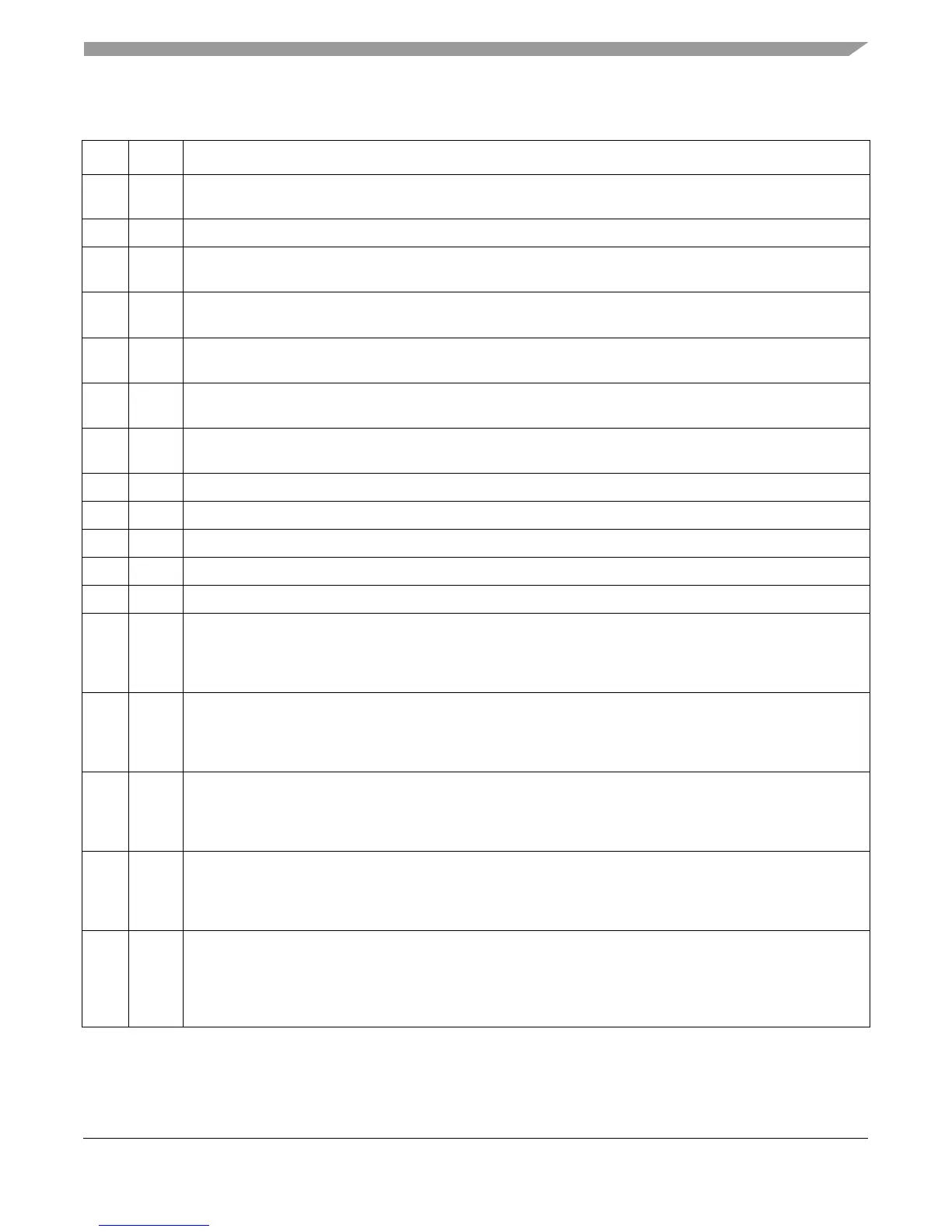

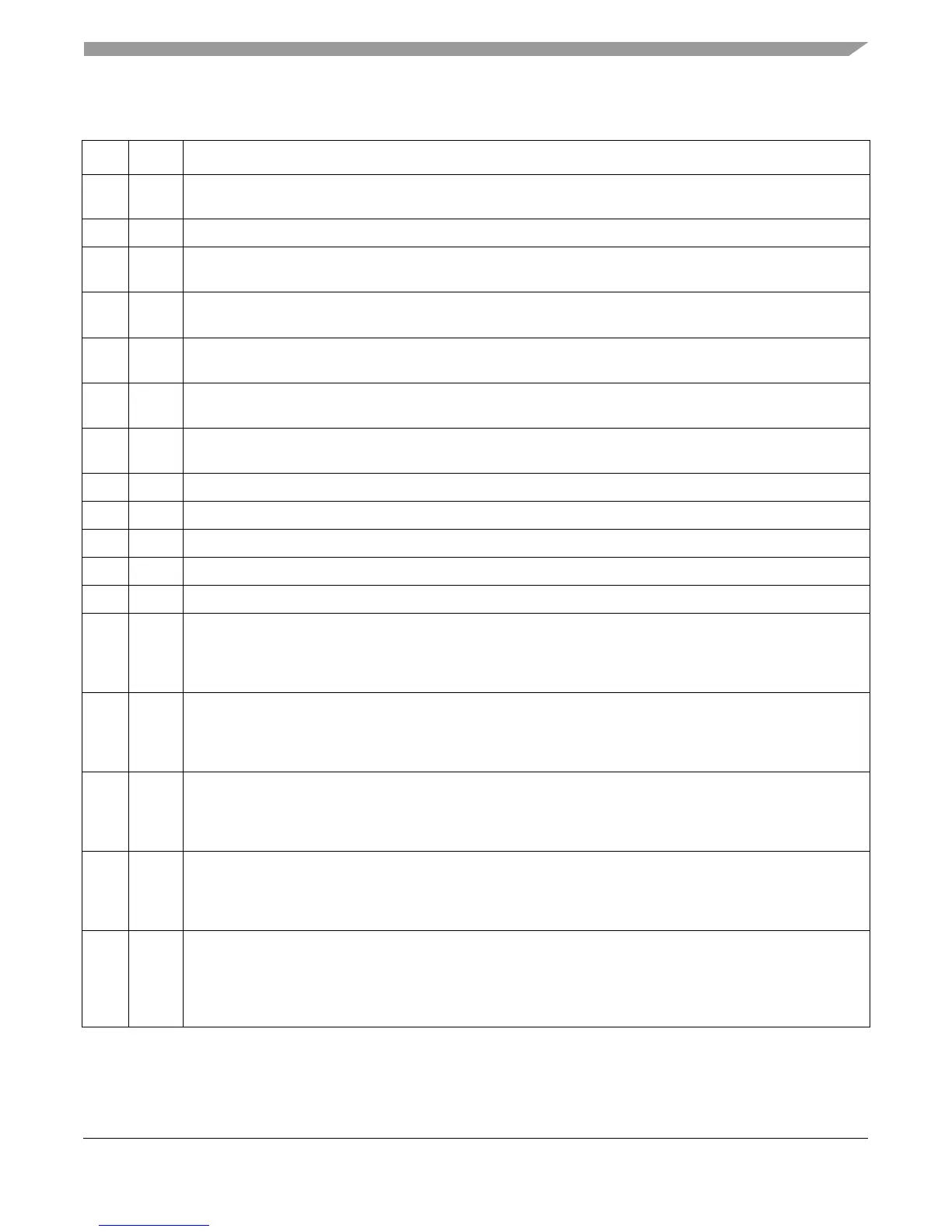

Register Model

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 2-51

46 FOVFS Embedded floating-point overflow sticky. Storage location for software to use when implementing true IEEE

floating point.

47 MODE Embedded floating-point mode (read-only on e500)

48 SOV Integer summary overflow. Set whenever an SPE instruction (except mtspr) sets OV. SOV remains set until it is

cleared by mtspr[SPEFSCR].

49 OV Integer overflow. An overflow occurred in the lower half of the register while a SPE integer instruction is being

executed.

50 FG Embedded floating-point guard bit. Floating-point guard bit from the lower half. The value is undefined if the

processor takes a floating-point exception due to input error, floating-point overflow, or floating-point underflow.

51 FX Embedded floating-point sticky bit. Floating bit from the lower half. The value is undefined if the processor takes

a floating-point exception due to input error, floating-point overflow or floating-point underflow.

52 FINV Embedded floating-point invalid operation error. Set when an input value on the high side is a NaN, Inf, or

Denorm. Also set on a divide if both the dividend and divisor are zero.

53 FDBZ Embedded floating-point divide-by-zero error. Set if the dividend is non-zero and the divisor is zero.

54 FUNF Embedded floating-point underflow error

55 FOVF Embedded floating-point overflow error

56 — Reserved, should be cleared.

57 FINXE Embedded floating-point inexact enable

58 FINVE Embedded floating-point invalid operation/input error exception enable.

0 Exception disabled

1 Exception enabled. A floating-point data exception is taken if FINV or FINVH is set by a floating-point

instruction.

59 FDBZE Embedded floating-point divide-by-zero exception enable

0 Exception disabled

1 Exception enabled. A floating-point data exception is taken if FDBZ or FDBZH is set by a floating-point

instruction

60 FUNFE Embedded floating-point underflow exception enable

0 Exception disabled

1 Exception enabled. A floating-point data exception is taken if FUNF or FUNFH is set by a floating-point

instruction.

61 FOVFE Embedded floating-point overflow exception enable

0 Exception disabled

1 Exception enabled. a floating-point data exception is taken if FOVF or FOVFH is set by a floating-point

instruction.

62–63 FRMC Embedded floating-point rounding mode control

00 Round to nearest

01 Round toward zero

10 Round toward +infinity

11 Round toward –infinity

Table 2-35. SPEFSCR Field Descriptions (continued)

Bits Name Function

Loading...

Loading...