PowerPC e500 Core Family Reference Manual, Rev. 1

3-4 Freescale Semiconductor

Instruction Model

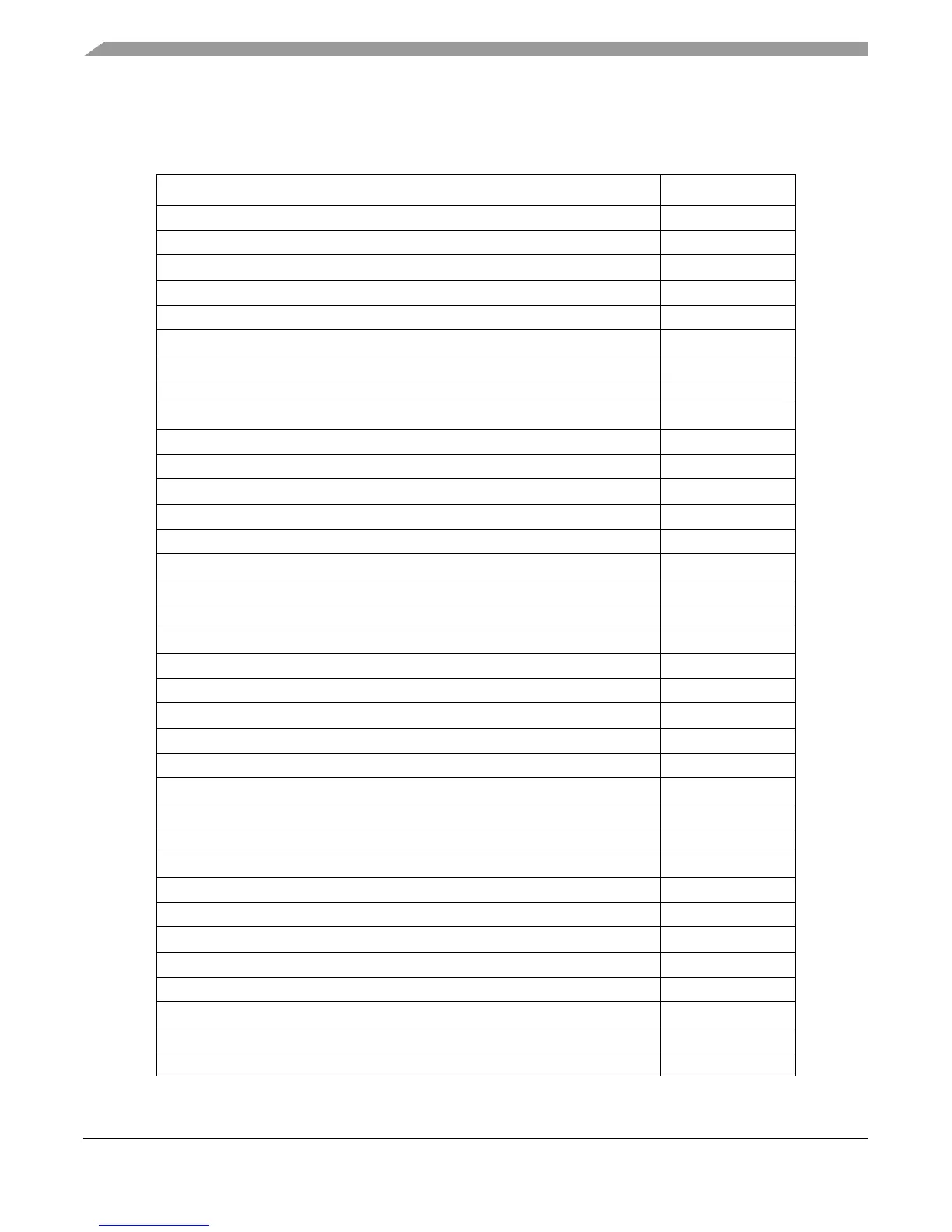

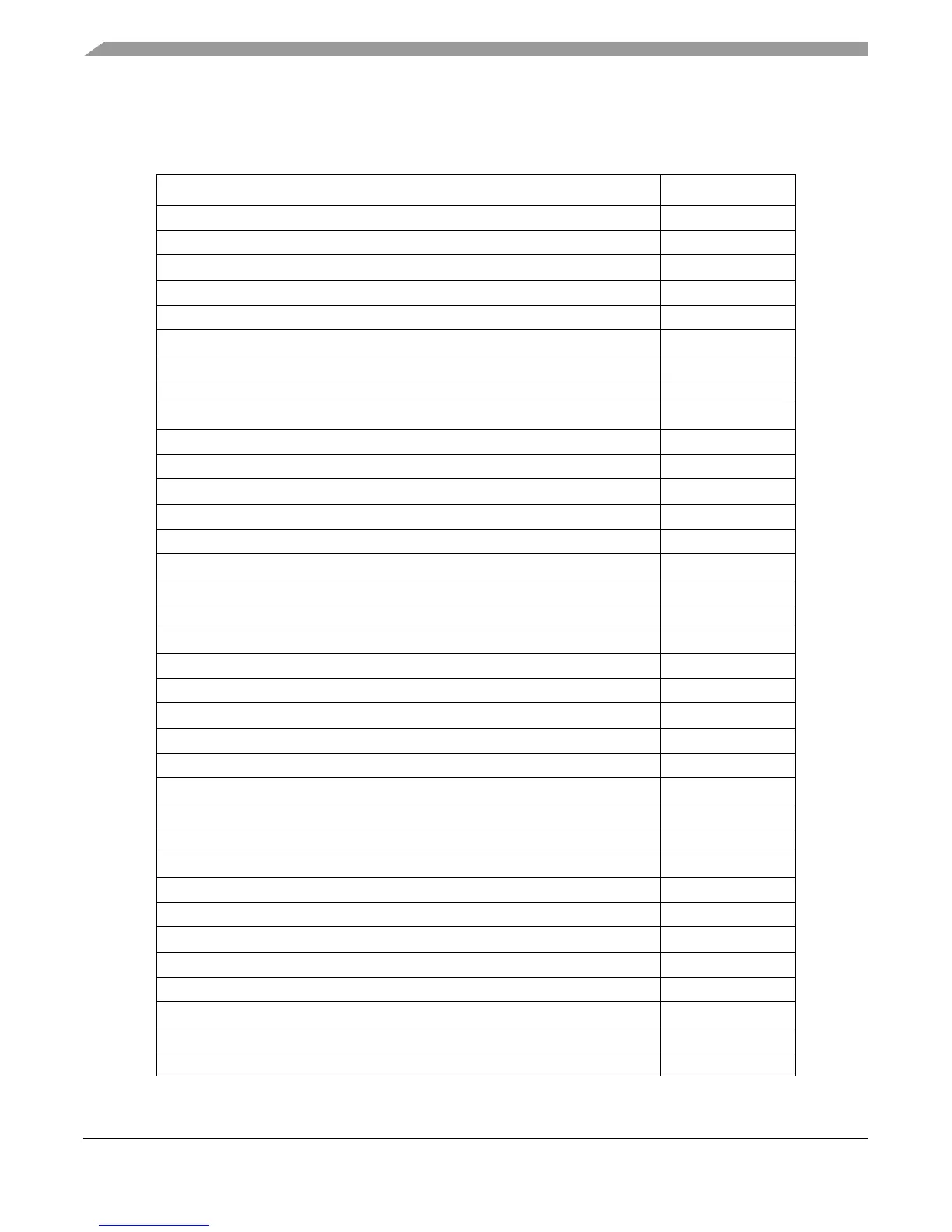

Table 3-2 lists 32-bit instructions that are not implemented in the e500.

Table 3-2. Unsupported Book E Instructions (32-Bit)

Name Mnemonic

Floating Absolute Value [and record CR] fabs[.]

Floating Add [Single] [and record CR] fadd[s][.]

Floating Convert From Integer Double Word fcfid

Floating Compare Ordered fcmpo

Floating Compare Unordered fcmpu

Floating Convert To Integer Double Word fctid

Floating Convert To Integer Double Word [and round to Zero] fctid[z]

Floating Convert To Integer Word [and round to Zero] [and record CR] fctiw[z][.]

Floating Divide [Single] [and record CR] fdiv[s][.]

Floating Multiply-Add [Single] [and record CR] fmadd[s][.]

Floating Move Register [and record CR] fmr[.]

Floating Multiply-Subtract [Single] [and record CR] fmsub[s][.]

Floating Multiply [Single] [and record CR] fmul[s][.]

Floating Negative Absolute Value [and record CR] fnabs[.]

Floating Negate [and record CR] fneg[.]

Floating Negative Multiply-Add [Single] [and record CR] fnmadd[s][.]

Floating Negative Multiply-Subtract [Single] [and record CR] fnmsub[s][.]

Floating Reciprocal Estimate Single [and record CR] fres[.]

Floating Round to Single-Precision [and record CR] frsp[.]

Floating Reciprocal Square Root Estimate [and record CR]

frsqrte[.]

Floating Select [and record CR] fsel[.]

Floating Square Root [Single] [and record CR] fsqrt[s][.]

Floating Subtract [Single] [and record CR] fsub[s][.]

Load Floating-Point Double [with Update] [Indexed] lfd[u][x]

Load Floating-Point Single [with Update] [Indexed] lfs[u][x]

Load String Word Immediate lswi

Load String Word Indexed lswx

Move From APID Indirect mfapidi

Move From Device Control Register mfdcr

Move From FPSCR [and record CR] mffs[.]

Move To Device Control Register mtdcr

Move To FPSCR Bit 0 [and record CR] mtfsb0[.]

Move To FPSCR Bit 1 [and record CR] mtfsb1[.]

Move To FPSCR Field [Immediate] [and record CR] mtfsf[i][.]

Store Floating-Point Double [with Update] [Indexed] stfd[u][x]

Loading...

Loading...