PowerPC e500 Core Family Reference Manual, Rev. 1

3-38 Freescale Semiconductor

Instruction Model

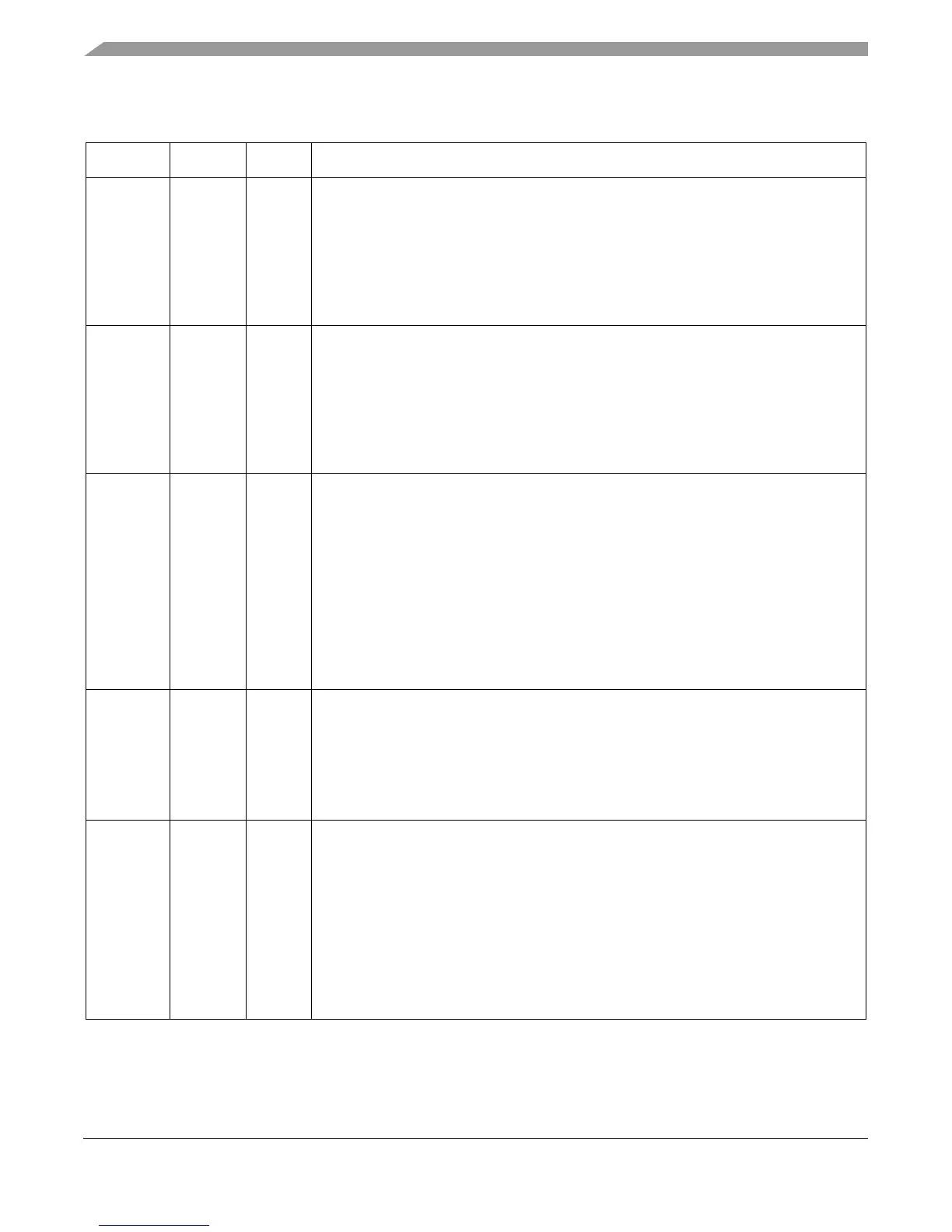

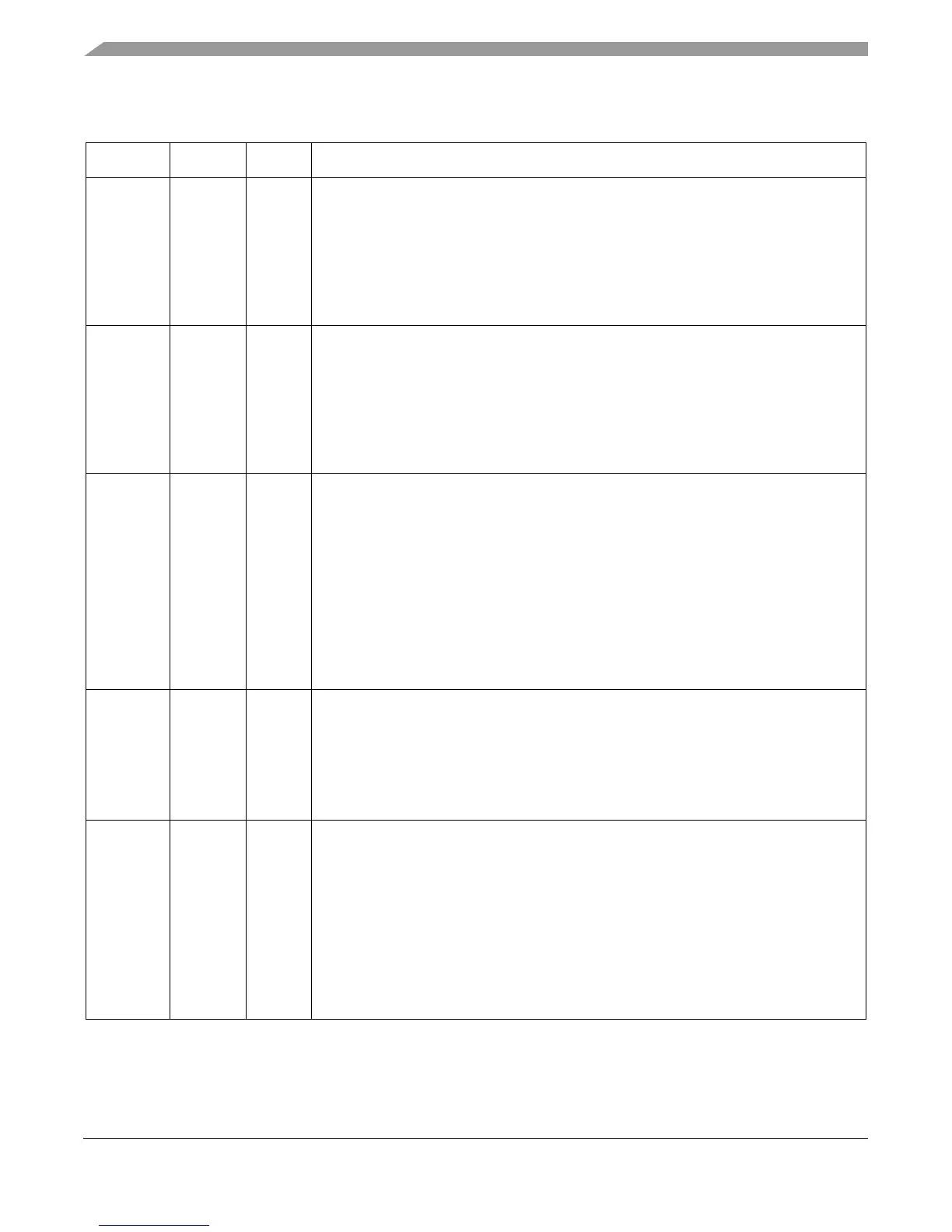

Table 3-26. User-Level Cache Instructions

Name Mnemonic Syntax Implementation Notes

Data Cache

Block

Allocate

dcba rA,rB The EA is computed, translated, and checked for protection violations. For cache hits, 32

bytes of zeros are written to the cache block and the tag is marked modified. For cache

misses with the replacement block marked non-dirty, a zero reload is performed and the

block is marked modified. However, if the replacement block is marked modified, the

contents are written back to memory first. If WIMG = xx1x (coherency enforced), the

address is broadcast to the bus before the zero reload fill.

A no-op occurs if the cache is disabled or locked, if the page is marked write-through or

cache-inhibited, or if a TLB protection violation occurs.

Data Cache

Block Flush

1

dcbf rA,rB The EA is computed, translated, and checked for protection violations:

• For cache hits with the tag marked modified, the cache block is written back to memory

and the cache entry is invalidated.

• For cache hits with the tag marked not modified, the entry is invalidated.

• For cache misses, no further action is taken.

A dcbf is broadcast if WIMG = xx1x (coherency enforced).dcbf acts like a load with

respect to address translation and memory protection. It executes in the LSU regardless

of whether the cache is disabled or locked.

Data Cache

Block Set to

Zero

1

dcbz rA,rB The EA is computed, translated, and checked for protection violations. For cache hits, 32

bytes of zeros are written to the cache block and the tag is marked modified. For cache

misses with the replacement block marked not modified, the zero reload is performed and

the cache block is marked modified. However, if the replacement block is marked modified,

the contents are written back to memory first. dcbz takes an alignment interrupt if the

cache is locked or disabled or if the cache is marked WT or CI. If WIMG = xx1x (coherency

enforced), the address is broadcast to the bus before the zero reload fill.

The interrupt priorities (from highest to lowest) are as follows:

1 Cache Is locked—alignment interrupt

2 Page marked write-through or cache-inhibited—alignment interrupt

3 TLB protection violation—data storage interrupt

dcbz is broadcast if WIMG = xx1x (coherency enforced).

Data Cache

Block Store

1

dcbst rA,rB The EA is computed, translated, and checked for protection violations.

• For cache hits with the tag marked not modified, no further action is taken.

• For cache hits with the tag marked modified, the cache block is written back to memory

and marked exclusive.

If WIMG = xx1x (coherency enforced) dcbst is broadcast. dcbst acts like a load with

respect to address translation and memory protection. It executes regardless of whether

the cache is disabled or locked.

Data Cache

Block Touch

2

dcbt CT,rA,rB dcbt allows potential performance enhancements through software-initiated prefetch

hints. Implementations are not required to take action based on execution of dcbt but can

prefetch the cache block corresponding to the EA into their cache. When dcbt executes,

the e500 checks for protection violations (as for a load instruction). dcbt is treated as a

no-op in the following cases:

• The access causes a protection violation.The page is mapped cache-inhibited.

• All lines that this entry maps to are locked or the cache is disabled.

• HID0[NOPTI] = 1

Otherwise, if no data is in the cache location, the e500 requests a cache line fill. Data

brought into the cache is validated as if it were a load instruction. The memory reference

of a dcbt sets the reference bit.

Loading...

Loading...