PowerPC e500 Core Family Reference Manual, Rev. 1

13-4 Freescale Semiconductor

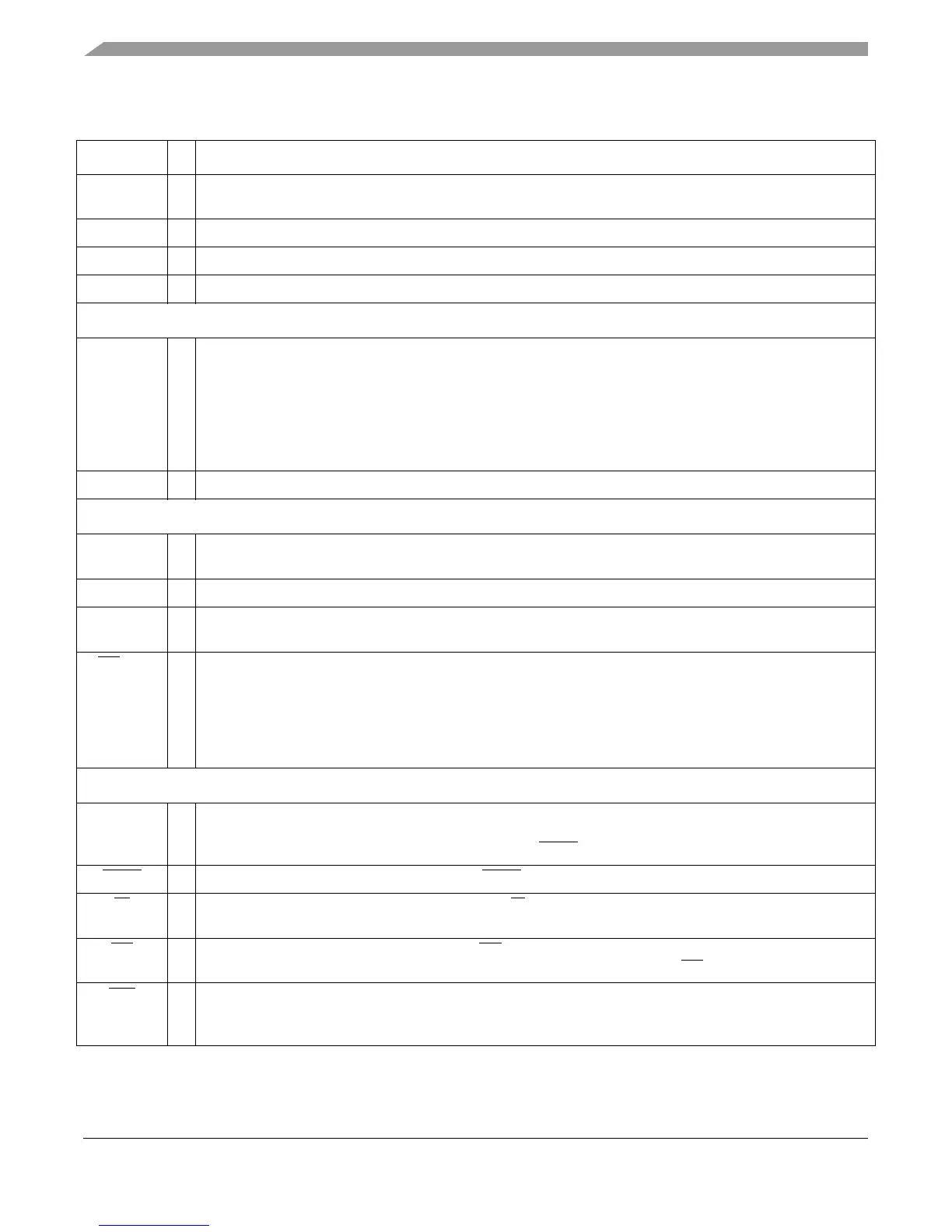

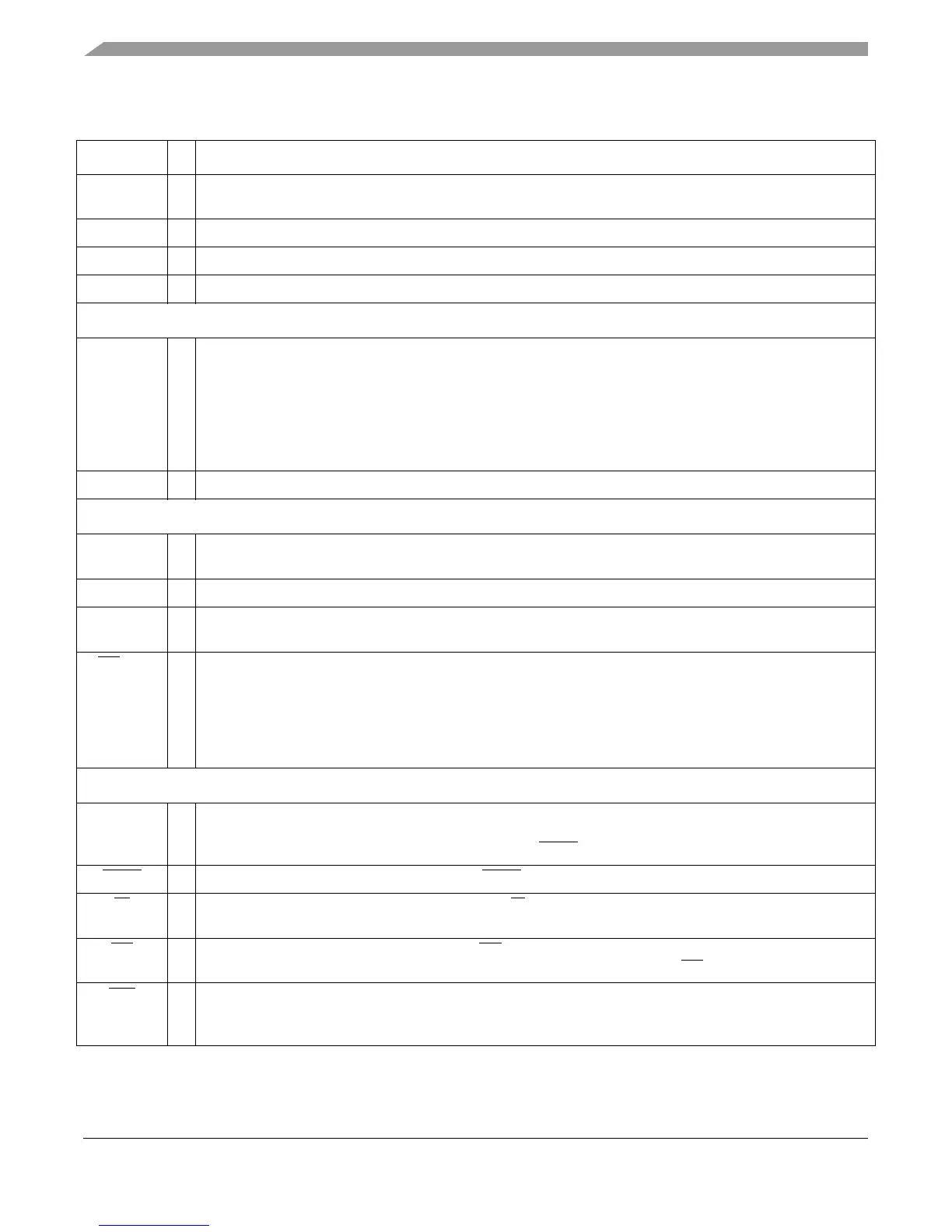

Core Complex Bus (CCB)

tdo

O JTAG test data output. The contents of the selected internal instruction or data register are shifted out onto

this signal on the falling edge of

tck

.

tdo_ien

O Test data out enable.

tdo

provides feedback to the external TAP linking module logic.

tlmsel

O TLM selected.

tlmsel

provides feedback to the external TAP linking module logic.

tap_en

I TAP enable.

tap_en

is used by the TAP linking module (TLM) logic external to the core complex.

Clocks

pll_cfg

[0:5] I PLL configuration select. Configurations are as follows:

00000_x PLL off

00001_0 or 00001_1 PLL 1x or 1.5x

00010_0 or 00010_1 PLL 2x or 2.5x

00011_0 or 00011_1 PLL 3x or 3.5x

00100_0 or 00100_1 PLL 4x or 4.5x

... similar pattern up to 24x for even multipliers, or 12.5x for odd multipliers.

pll_clk

I PLL clock. Clock reference for the CCB.

Time Base

tbclk

I Sampled by the system logic to CCB clock. Required to be no more than 1/4 platform clock frequency. If

selected, it can be a source of the time base.

tben

I Asserted by the system logic to enable the time base

tbint

O Asserted when a time base interrupt is signaled. This ordinarily prompts external logic to bring the core out of

power-down mode by negating

stop

and then

halt

so the interrupt can be serviced.

wrs

[0:1] O Watchdog timer reset status. These two bits are set to one of three values when a reset is caused by the

watchdog timer. These bits are undefined at power-up.

00 Implementation-dependent reset information.

01 Implementation-dependent reset information.

10 Implementation-dependent reset information.

11 Idle

External Interrupts

hreset_req

O Hard reset request. When DBCRO[RST] is set, the core sends an HRESET_REQ to the system. The system

recognizes the assertion of this request and then stops the core using power management. With hreset_req

being asserted and the core being in STOPPED state,

hreset

is asserted and core flushing starts.

hreset

I Hard reset. Assertion flushes the core. When

hreset

is negated, the 256 CCB clocks core flush starts.

int

I External interrupt. Initiates an external interrupt. If

int

is asserted and MSR[EE] is set, the e500 vectors to

IVOR4.

cint

I Critical interrupt. Initiates a critical interrupt. If

cint

is asserted and MSR[CE] is set, the e500 vectors to IVOR0.

If MSR[CE] is 0, critical interrupts are disabled and the e500 does not sample

cint

.

mcp

I Machine check interrupt. Initiates a machine check operation. If MSR[ME] is set, the e500 vectors to IVOR1.

If MSR[ME] is clear, then the e500 goes into checkstop state. MCSR is updated as defined in Section 2.7.2.4,

“Machine Check Syndrome Register (MCSR).”

Table 13-1. Summary of Selected Internal Signals (continued)

Signal I/O Comments, or Meaning when Asserted

Loading...

Loading...