PowerPC e500 Core Family Reference Manual, Rev. 1

C-32 Freescale Semiconductor

Simplified Mnemonics for PowerPC Instructions

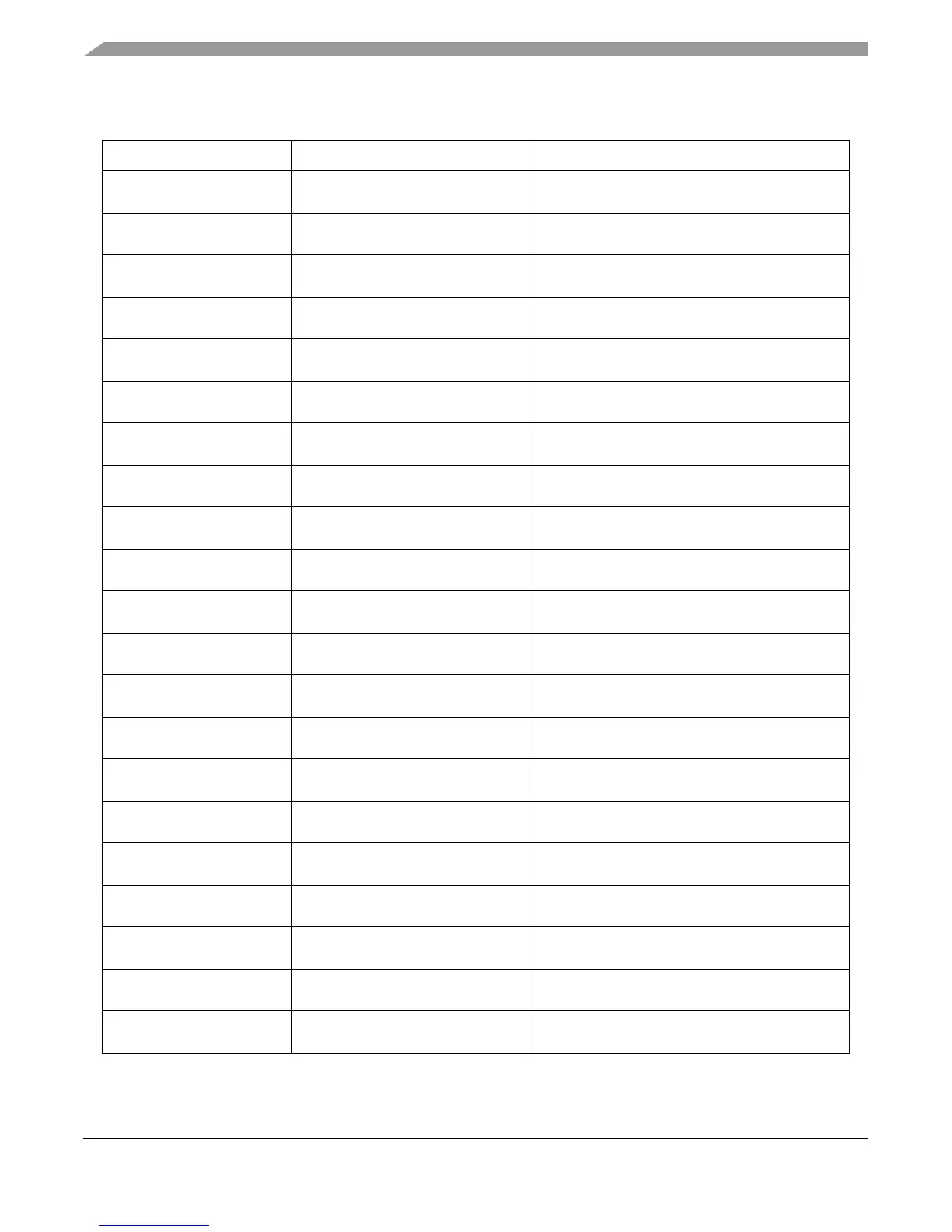

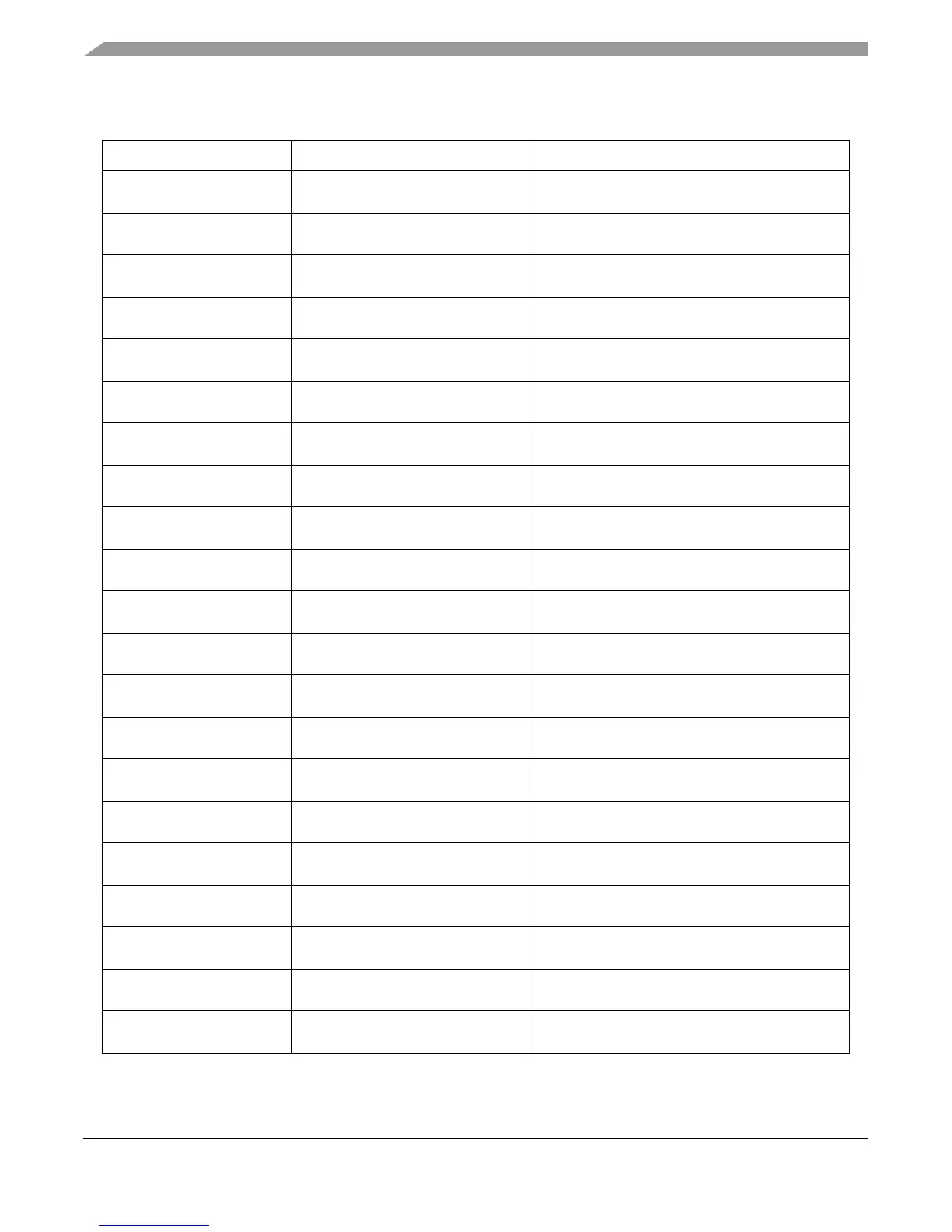

bnsctr crS target bcctr 4,BI

6

,target Branch if not summary overflow (bcctr without

comparison conditions and LR updating)

bnsctrl crS target bcctrl 4,BI

6

,target Branch if not summary overflow (bcctrl with

comparison conditions and LR update)

bnsl crS target bcl 4,BI

6

,target Branch if not summary overflow (bcl with

comparison conditions and LR updating)

bnsla crS target bcla 4,BI

6

,target Branch if not summary overflow (bcla with

comparison conditions and LR updating)

bnslr crS target bclr 4,BI

6

,target Branch if not summary overflow (bclr without

comparison conditions and LR updating)

bnslrl crS target bclrl 4,BI

6

,target Branch if not summary overflow (bclrl with

comparison conditions and LR update)

bnu crS target bc 4,BI

6

,target Branch if not unordered (bc without comparison

conditions or LR updating)

bnua crS target bca 4,BI

6

,target Branch if not unordered (bca without comparison

conditions or LR updating)

bnuctr crS target bcctr 4,BI

6

,target Branch if not unordered (bcctr without comparison

conditions and LR updating)

bnuctrl crS target bcctrl 4,BI

6

,target Branch if not unordered (bcctrl with comparison

conditions and LR update)

bnul crS target bcl 4,BI

6

,target Branch if not unordered (bcl with comparison

conditions and LR updating)

bnula crS target bcla 4,BI

6

,target Branch if not unordered (bcla with comparison

conditions and LR updating)

bnulr crS target bclr 4,BI

6

,target Branch if not unordered (bclr without comparison

conditions and LR updating)

bnulrl crS target bclrl 4,BI

6

,target Branch if not unordered (bclrl with comparison

conditions and LR update)

bso crS target bc 12,BI

6

,target Branch if summary overflow (bc without

comparison conditions or LR updating)

bsoa crS target bca 12,BI

6

,target Branch if summary overflow (bca without

comparison conditions or LR updating)

bsoctr crS target bcctr 12,BI

6

,target Branch if summary overflow (bcctr without

comparison conditions and LR updating)

bsoctrl crS target bcctrl 12,BI

6

,target Branch if summary overflow (bcctrl with

comparison conditions and LR update)

bsol crS target bcl 12,BI

6

,target Branch if summary overflow (bcl with comparison

conditions and LR updating)

bsola crS target bcla 12,BI

6

,target Branch if summary overflow (bcla with comparison

conditions and LR updating)

bsolr crS target bclr 12,BI

6

,target Branch if summary overflow (bclr without

comparison conditions and LR updating)

Table C-29. Simplified Mnemonics (continued)

Simplified Mnemonic Mnemonic Instruction

Loading...

Loading...