PowerPC e500 Core Family Reference Manual, Rev. 1

2-8 Freescale Semiconductor

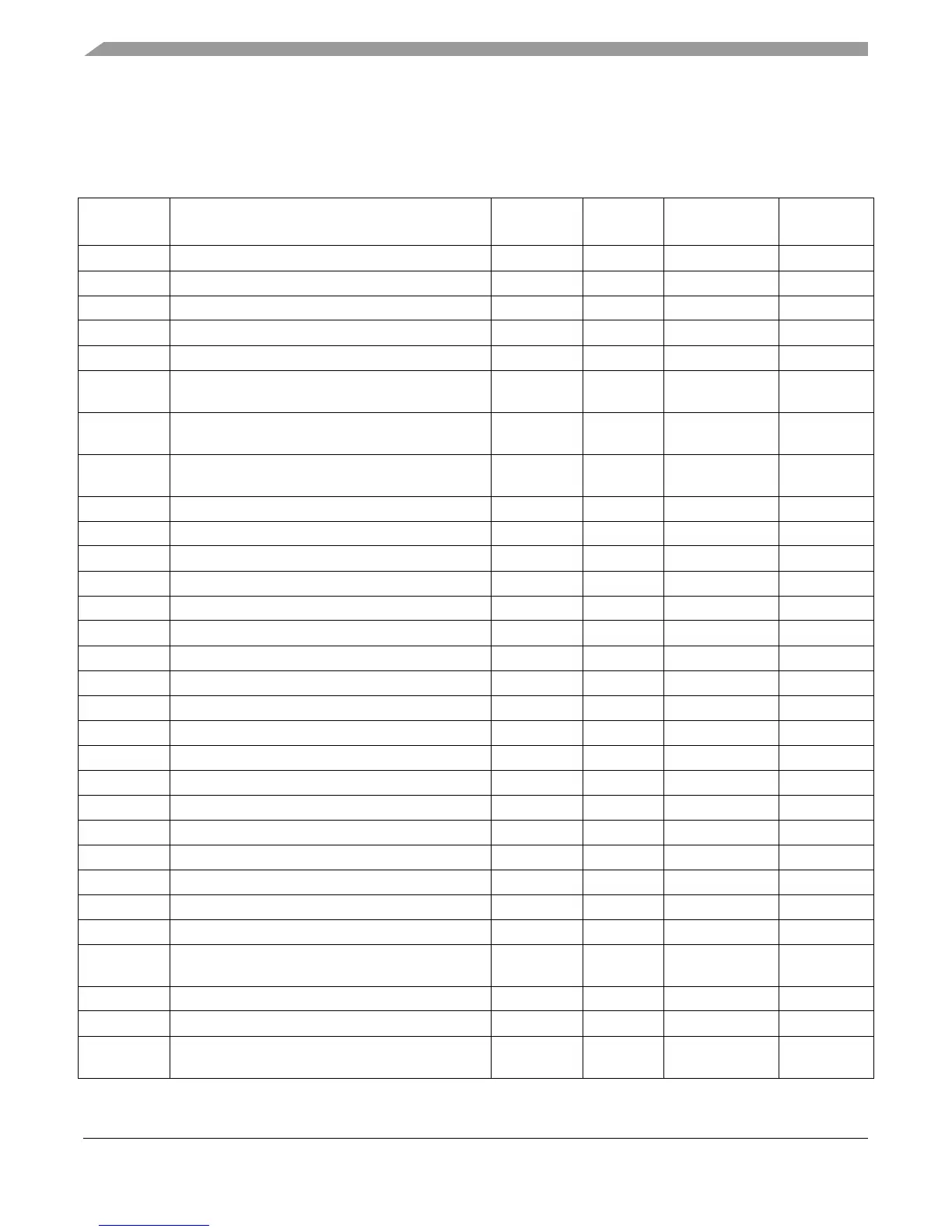

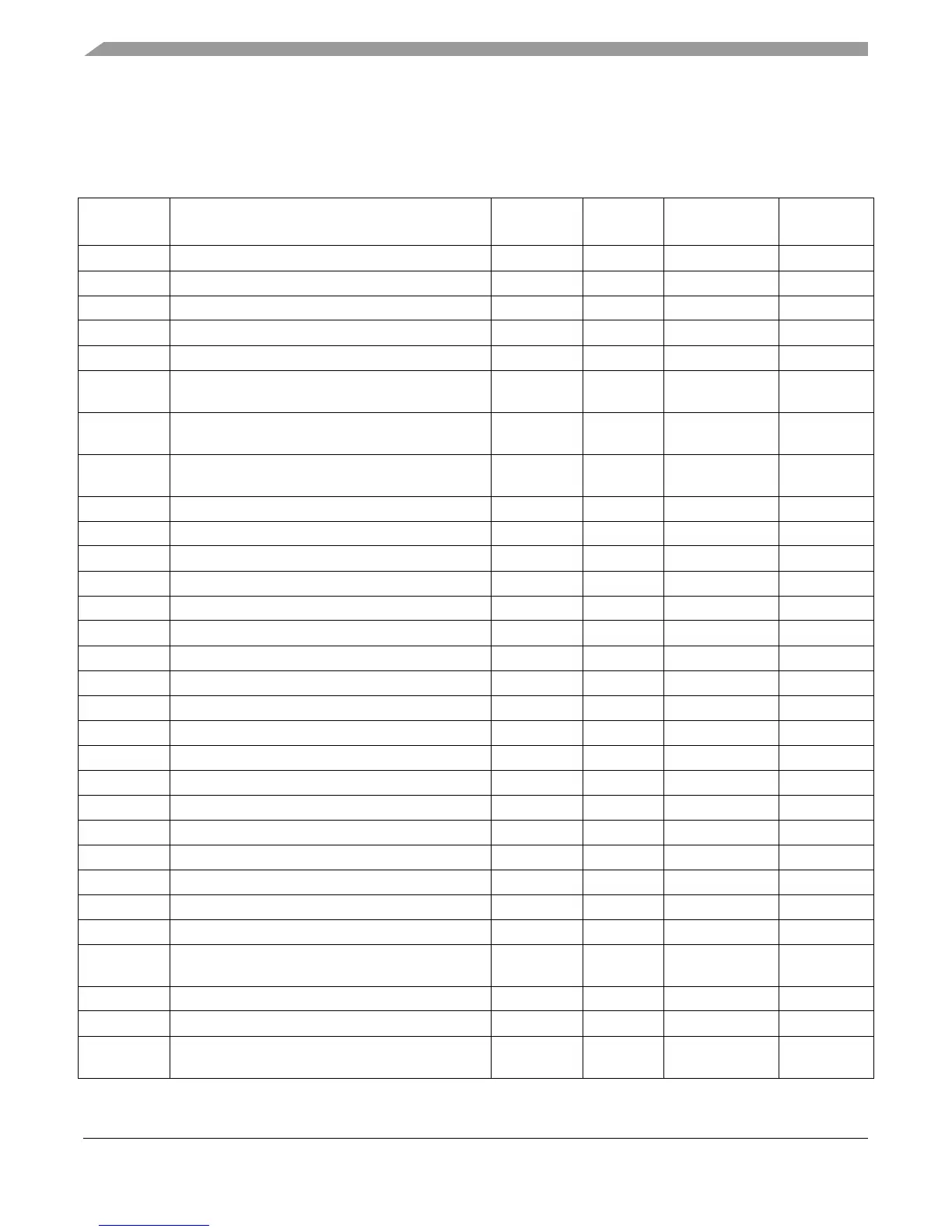

Register Model

Table 2-2 describes the implementation-specific SPRs of the core complex. Compilers should

recognize the mnemonic name given in Table 2-2 when parsing instructions.

Table 2-2. Implementation-Specific SPRs (by SPR Abbreviation)

SPR

Abbreviation

Name SPR Number Access Supervisor Only Section/Page

BBEAR Branch buffer entry address register

1

513 Read/Write No 2.9.1/2-25

BBTAR Branch buffer target address register

1

514 Read/Write No 2.9.2/2-25

BUCSR Branch unit control and status register

1

1013 Read/Write Yes 2.9.3/2-26

HID0 Hardware implementation dependent register 0

1

1008 Read/Write Yes 2.10.1/2-27

HID1 Hardware implementation dependent register 1

1

1009 Read/Write Yes 2.10.1/2-27

IVOR32 SPE/embedded floating-point APU unavailable

interrupt offset

528 Read/Write Yes 2.7.1.5/2-19

IVOR33 Embedded floating-point data exception interrupt

offset

529 Read/Write Yes 2.7.1.5/2-19

IVOR34 Embedded floating-point round exception interrupt

offset

530 Read/Write Yes 2.7.1.5/2-19

IVOR35 Performance monitor 531 Read/Write Yes 2.7.1.5/2-19

L1CFG0 L1 cache configuration register 0 515 Read-only No 2.11.3/2-34

L1CFG1 L1 cache configuration register 1 516 Read-only No 2.11.4/2-35

L1CSR0 L1 cache control and status register 0

1

1010 Read/Write Yes 2.11.1/2-31

L1CSR1 L1 cache control and status register 1

1

1011 Read/Write Yes 2.11.2/2-33

MAS0 MMU assist register 0

1

624 Read/Write Yes 2.12.5.1/2-40

MAS1 MMU assist register 1

1

625 Read/Write Yes 2.12.5.2/2-41

MAS2 MMU assist register 2

1

626 Read/Write Yes 2.12.5.3/2-42

MAS3 MMU assist register 3

1

627 Read/Write Yes 2.12.5.4/2-43

MAS4 MMU assist register 4

1

628 Read/Write Yes 2.12.5.5/2-43

MAS6 MMU assist register 6

1

630 Read/Write Yes 2.12.5.6/2-44

MAS7 MMU assist register 7

1

944 Read/Write Yes 2.12.5.7/2-45

MCAR Machine check address register 573 Read-only Yes 2.7.2.3/2-22

MCSR Machine check syndrome register 572 Read/Write Yes 2.7.2.4/2-23

MCSRR0 Machine-check save/restore register 0 570 Read/Write Yes 2.7.2.1/2-22

MCSRR1 Machine-check save/restore register 1 571 Read/Write Yes 2.7.2.2/2-22

MMUCFG MMU configuration register 1015 Read-only Yes 2.12.3/2-37

MMUCSR0 MMU control and status register 0

1

1012 Read/Write Yes 2.12.2/2-36

PID0 Process ID register 0. Book E defines only this PID

register and refers to as PID, not PID0.

1

48 Read/Write Yes 2.12.1/2-36

PID1 Process ID register 1

1

633 Read/Write Yes 2.12.1/2-36

PID2 Process ID register 2

1

634 Read/Write Yes 2.12.1/2-36

SPEFSCR Signal processing and embedded floating-point

status and control register

1

512 Read/Write No 2.14.1/2-49

Loading...

Loading...