Intel

®

EP80579 Integrated Processor Product Line—Layout Checklist

Intel

®

EP80579 Integrated Processor Product Line

Platform Design Guide May 2010

276 Order Number: 320068-005US

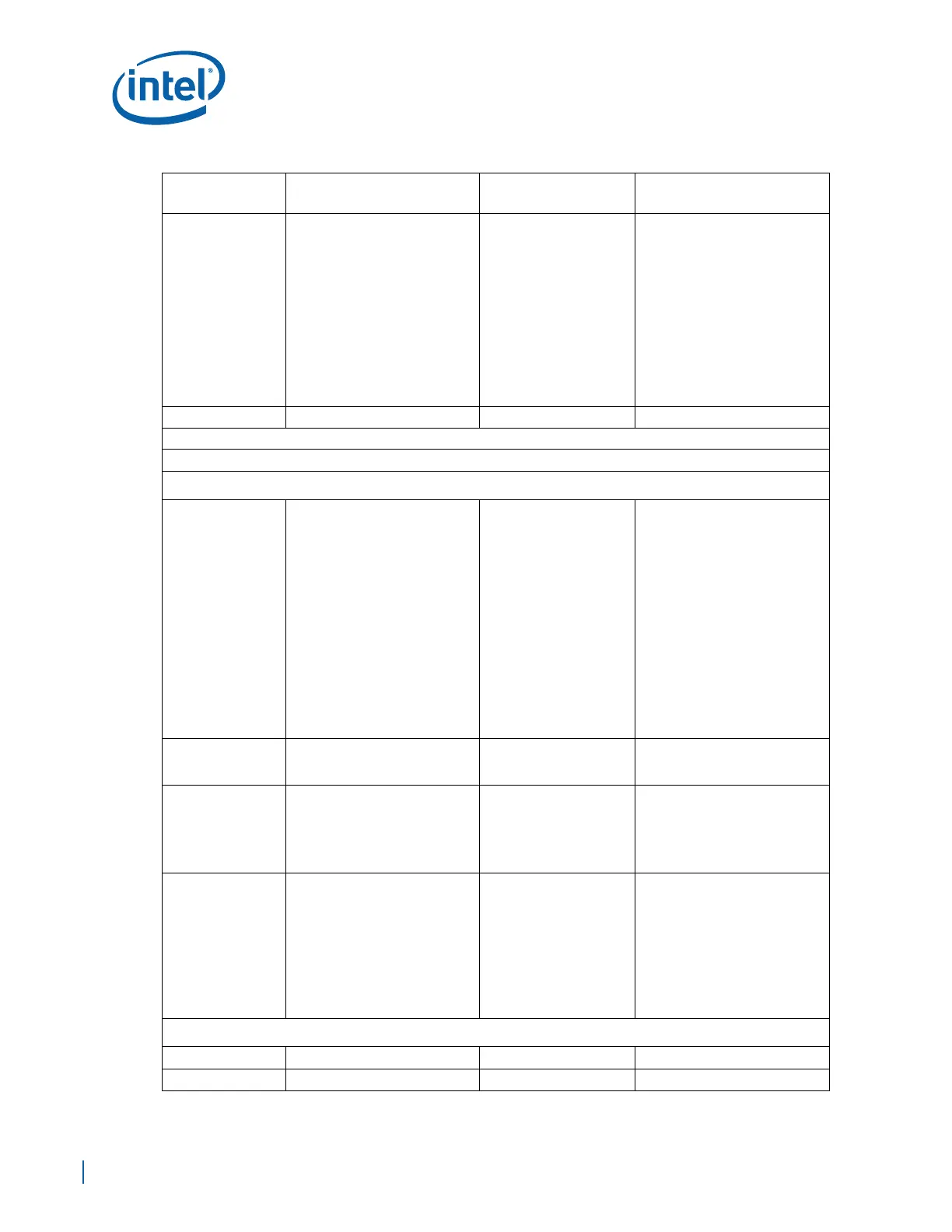

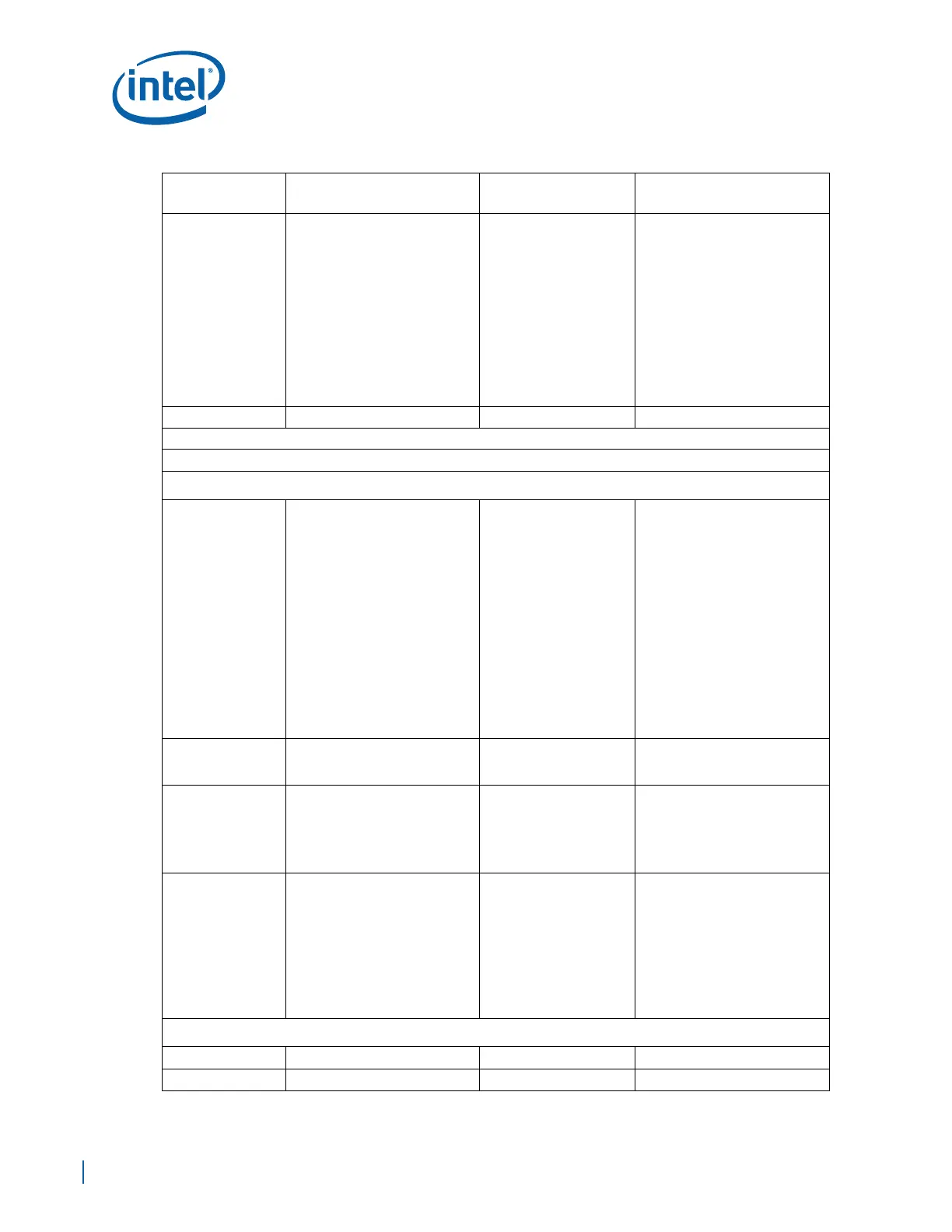

SATA_CLKREFp,

SATA_CLKREFn

Zdiff = 100

Ω +/- 10%

Trace Width:

Brakeout Trace Width 4 mils

Microstrip: 4 mils

Stripline: 3.75 mils (L3/L8)

Airgap Spacing:

Brakeout spacing Min=4mils

Microstrip: 6 mils

Stripline: 9 mils

Spacing between Pairs 20mils

Spacing to other signals 20 mils

Serpentine Spacing 20 mils

Routing Length LT:

Min = 1 in.

Max = 16 in.

Inter-pair length

matching: +/- 5 mils

See Section 8.2.2, “CLK100 (SRC

Clock) Group”.

2 Vias Max

SATALED# Zo = 50

Ω +/- 10%

SATA0GP (GP26_SATA0GP) See General Purpose I/O (GPIO) Interface

SATA1GP (GP29_SATA1GP) See General Purpose I/O (GPIO) Interface

Universal Serial Bus (USB) Interface

USBp[1:0],

USBn[1:0]

Zdiff = 90

Ω +/- 10%

Trace Width:

Brakeout Trace Width 4 mils

Microstrip: 4.75 mils

Stripline: 4.5 mils

Airgap Spacing:

Brakeout spacing Min=4mils

Microstrip: 5.25 mils

Stripline: 5.5 mils

Spacing between Pairs

Min = 45mils

Spacing to clock signals

Min = 45mils

Spacing to non clock signals

Min = 45mils

Breakout:

Max = 400mils.

Board Length:

Microstrip 2-11 in.

Strip Line 2-10 in.

Inter-pair length

matching

Max = 60 mils skew

See Section 12.2.2, “USB

Differential Signals – USBp[1:0],

USBn[1:0]”.

Keep all traces as short as

possible. Choke must be placed

as close as possible to the

connector.

OC[1:0]# Zo = 50

Ω +/- 10%

•See Section 12.2.5, “USB

Over Current protection –

OC[1:0]#”.

USB_RBIASp

USB_RBIASn

Zo = 50

Ω +/- 10%

Length LT:

Max = 0.5 in.

•See Section 12.2.3,

“USB_RBIASp/USB_RBIASn

Connection”.

•Place the

22.6 Ω resistor

within 0.5 in. of the

EP80579.

CLK48

Zo = 50

Ω +/- 10%

Trace Width

Microstrip: 5.5 mils

Stripline: 4.5 mils (L3)

Airgap Spacing:

Spacing to other signals

Min = 20mils

Spacing to non clock signals

Min = 45mils

Length LT:

2 to 20 in

Place damping resistor as close

as possible to the source.

Power Management Interface

PLTRST# Zo = 50

Ω +/- 10%

PROCHOT# Zo = 50

Ω +/- 10%

Table 97. Layout Checklist (Sheet 8 of 13)

Signal Name

Trace Geometry and

Impedance

Length Requirements Comments

Loading...

Loading...