Intel

®

EP80579 Integrated Processor Product Line May 2010

Order Number: 320068-005US 298

Schematics Checklist—Intel

®

EP80579 Integrated Processor Product Line

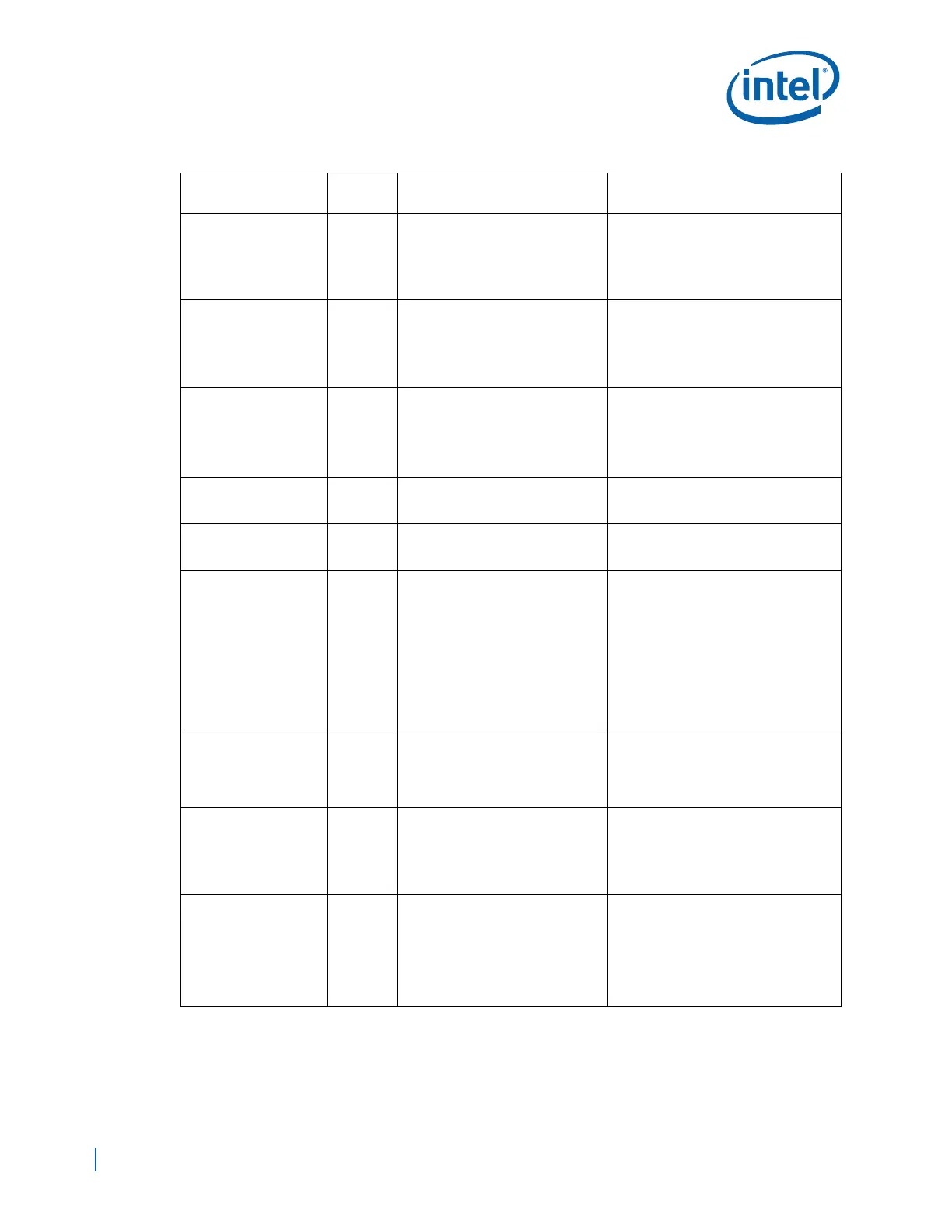

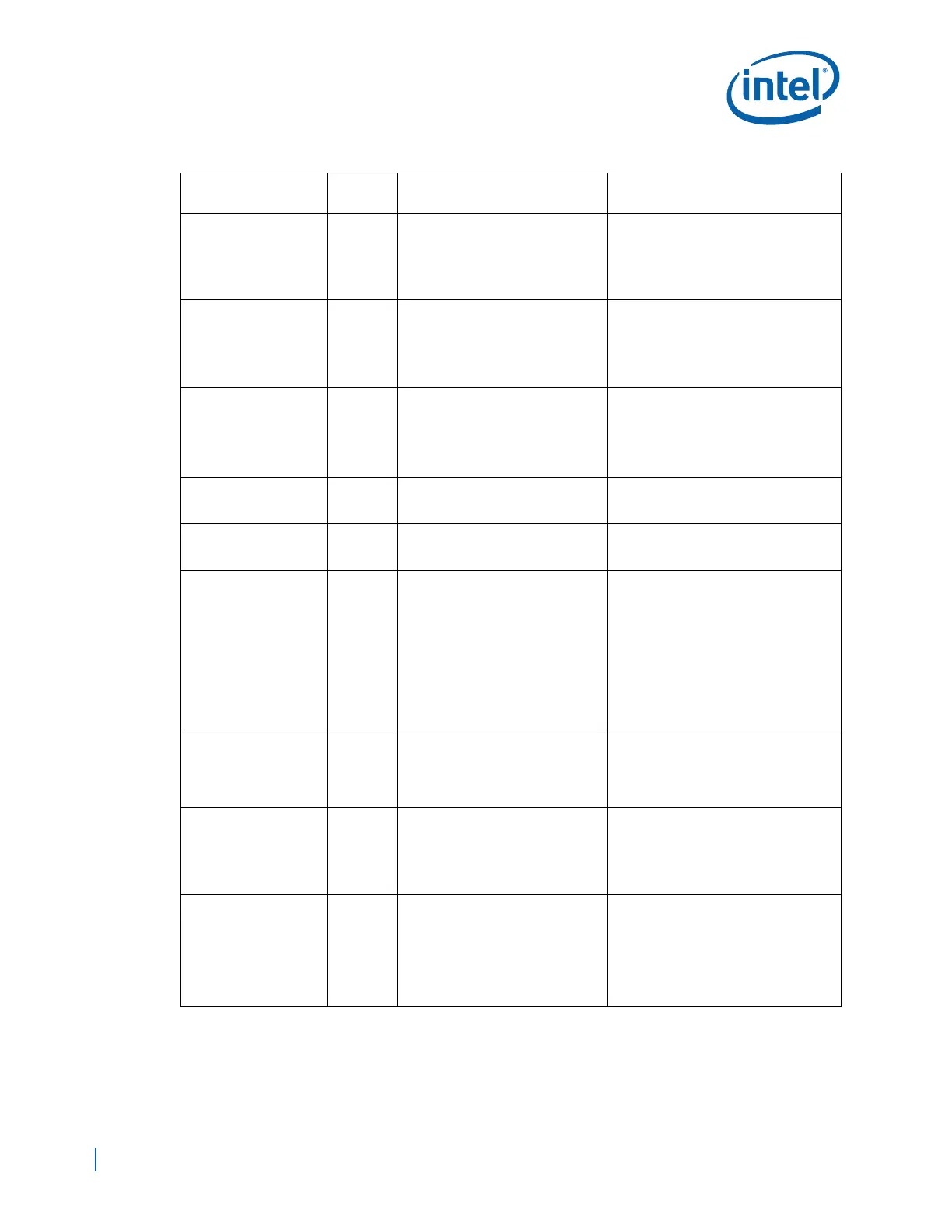

PROCHOT# O

• Can monitor using an LED to

indicate IA-32 core Thermal

Status.

• Pull up signal to EP80579

VCC33 (3.3V)

using a 10KΩ ±

5%

resistors

Thermal Alarm. Driven out by EP80579.

Monitored by Platform.

THRMTRIP# OD I/O

• Monitor using an LED to

indicate IA-32 core Thermal

Status.

• Pull up signal to EP80579

VCC33 (3.3V)

using a 10KΩ ±

5%

resistors

Thermal Trip. When Low, immediately

transitions IICH to S5 State

SLP_S3#

SLP_S4#,

SLP_S5#

O

• Signals are driven by EP80579

to Platform Sleep logic.

• Can monitor any or all the

signals using LEDs to indicate

IA-32 core Sleep Status

• S3 Sleep Control (Power Down):

Suspend-To_RAM (STR)

• S4 Sleep Control (Power Down):

Suspend-To-DISK

• S5 Sleep Control (Power Down):

S5-Soft Off

PWROK I

• Connect to Platform

SYS_PWR_OK

Indicates EP80579 core power

(VRMPWRGD) has been stable for a

minimum of 99ms.

SYS_PWR_OK I

• Connect to Platform

SYS_PWR_OK

Indicates EP80579 core power

(VRMPWRGD) has been stable for a

minimum of 99ms.

PWRBTN# I

• Direct connect to front panel

power button on system

• Power Button: Causes system to go

to a sleep state. If already in sleep

state, will cause a wake event. If

PWRBTN# is pressed for more than

four seconds, will cause

unconditional transition (power

button override) to the S5 state.

Override will occur even if the

system is in the S3 or S4 state.

• This signal has a 50 KΩ internal

pullup resistor and has an internal

16 ms de-bounce on the input

RI# I

• This signal is not implemented.

• Pull-up to EP80579 3.3V

Standby (VCCPSUS) power

supply using 10KΩ ± 5%

resistor.

• Ring Indicate: From the modem

interface. Can be enabled as a wake

event and is preserved during

power failures

SYS_RESET# I

• Connect to front panel Reset

Button on system.

• Pull-up to Platform 3.3V

Standby (VSBY3_3) power

supply using 10KΩ ± 5%

resistor.

• System Reset: Forces internal reset.

• Signal should not float.

• Requires external pull-up.

RSMRST# I

• Connect to SuperIO (SIO)

RSMRST# output and must go

high no sooner than 10 ms

after VSBY3_3 has reached

their nominal voltages.

• Connect through 8.2

kΩ ± 5%

resistor to GND.

• Resume Well Reset. This signal is

used to reset the Suspend power

plane logic.

• If the SIO device is not used in the

design, an external RC circuit is

required to guarantee that the

resume well power is valid prior to

RSMRST# going high.

Table 100. Schematic Checklist (Sheet 15 of 26)

Checklist Items

I/O Type

(Default)

Recommendations Comments

Loading...

Loading...