Intel

®

EP80579 Integrated Processor Product Line May 2010

Order Number: 320068-005US 308

Schematics Checklist—Intel

®

EP80579 Integrated Processor Product Line

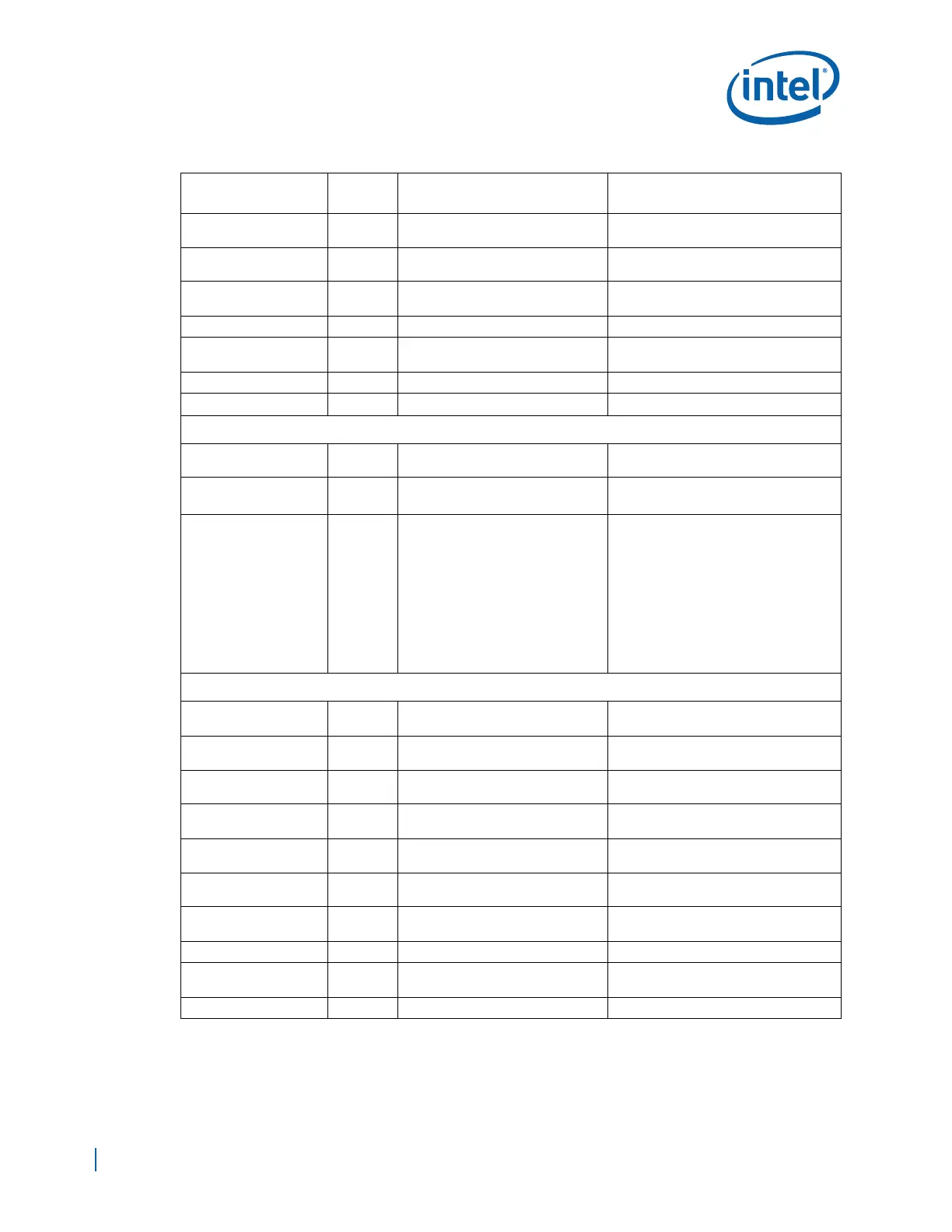

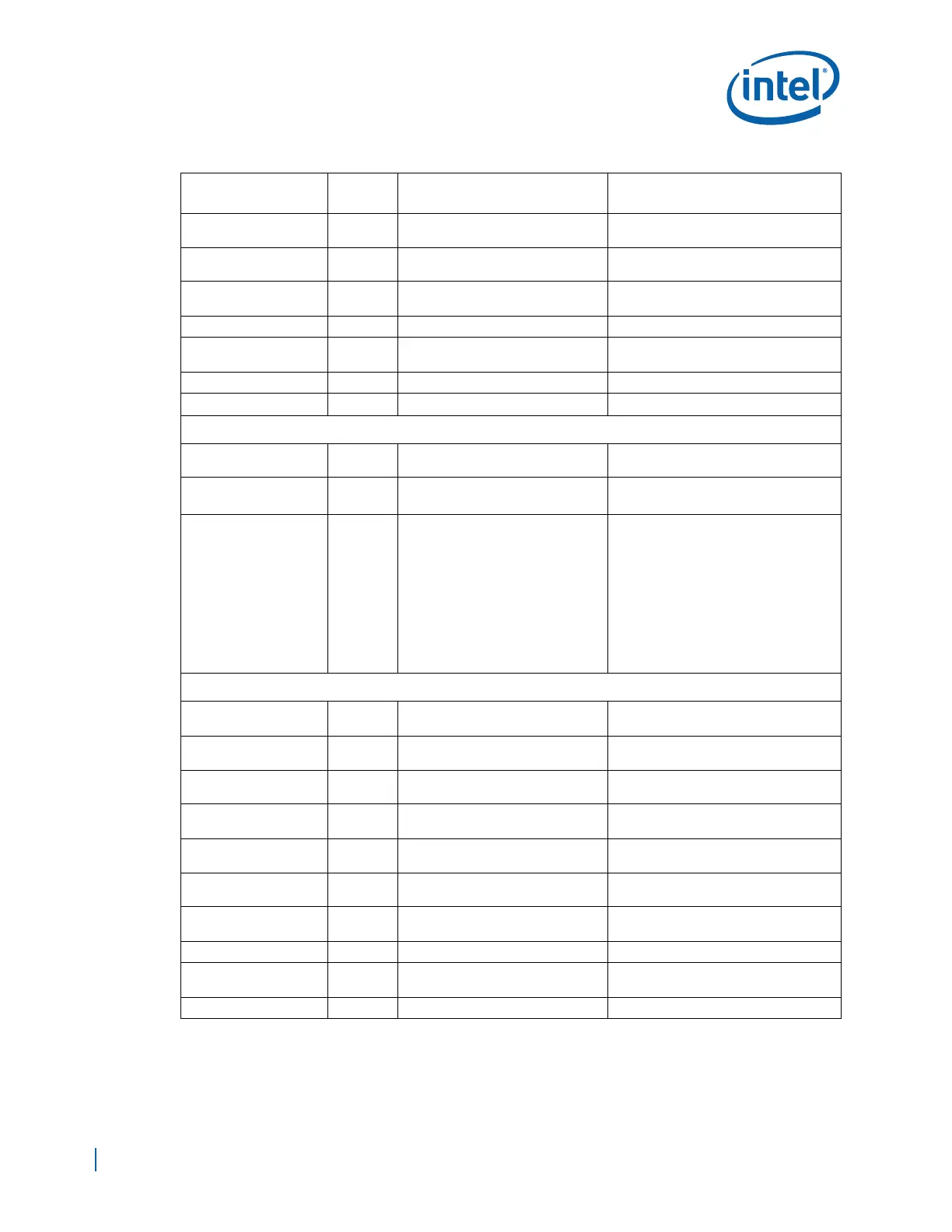

TDO

Pull-up to Platform 1.2V (V1P2)

supply through a 51Ω ±5% resistor

TMS

Pull-up to Platform 1.2V (V1P2)

supply through a 51Ω ±5% resistor

TRST#

Pull-down to ground through a 51Ω

±5% resistor

BPM3_IN I No connect

BPM4_PRDY_OUT OD No external pull-up required

•See Section 26.3.2.2 for more

details.

BPM5_PREQ_IN I No connect

BPM[3:0] I/O No connect

Miscellaneous Pins

PME# I/O OD

Connect to EP80579 GBE_WAKE

output

• 50KΩ internal pull-up

PCIRST# O

• Leave as no connect.

• Use PLTRST# for system reset

See Section 7.2 and Figure 49 for more

details

SPKR O

No Reboot Strap:

The SPKR signal is sampled at

Platform Reset as a functional

strap:

• This strap controls the re-boot

behavior of timeouts in the TCO

Timer

• 0 = Reboot on second timeout

of TCO timer (default)

• 1 = No re-boot on second

timeout of TCO Timer

SPKR:

• This signal drives an external

speaker driver device, which in turn

drives the system speaker. Upon

PLTRST#, its output state is 0.

• Weak internal pull-down

Reserved Pins

Reserved0

Must have external 10KΩ pull-down

to VSS

Reserved1

Must have external 10KΩ pull-down

to VSS

Reserved2

Must have external 10KΩ pull-down

to VSS

Reserved3

Must have external 10KΩ pull-down

to VSS

Reserved4

Must have external 10KΩ pull-down

to VSS

Reserved5

Must have external 10KΩ pull-down

to VSS

Reserved6

Must have external 10KΩ pull-down

to VSS

Reserved7 Must be connected to VSS

Reserved8

Must have external 10KΩ pull-down

to VSS

Reserved9 Must be connected to VSS

Table 100. Schematic Checklist (Sheet 25 of 26)

Checklist Items

I/O Type

(Default)

Recommendations Comments

Loading...

Loading...