Large Segment OffloadBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 112

The ISO related registers are to allow for processing of ISO Ethernet Audio Video (EAV)-related TX traffic. A

physically separate isochronous TX queue exists in some Broadcom Ethernet controllers to support audio/video

traffic applications, which require very precisely timed isochronous launch of TX packets onto the wire.

Send Buffer Descriptor

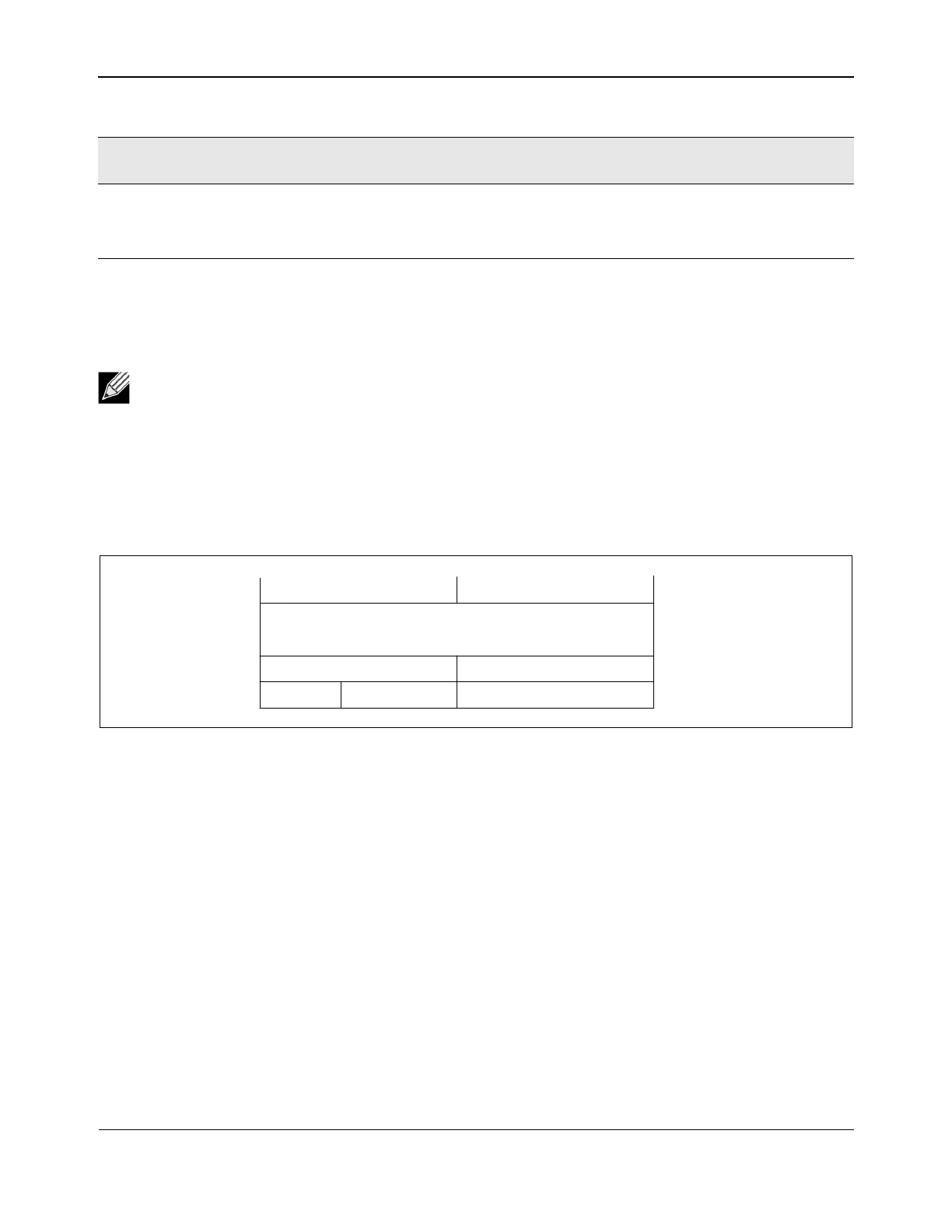

The Send Buffer Descriptor (SBD) diagram is shown below.

Figure 22: Send Buffer Descriptor

Host Address

This field is a 64-bit address specifying where the Send Buffer is located in Host memory.

Length[15:0]

This field is the length of the frame or TCP large segment to be transmitted.

VLAN Tag[15:0]

This field is the VLAN Tag to be inserted into the frame if Flags[6] is set to 1.

HdrLen[7:0]

This field is the length of the Ether + IP + TCP Headers to be replicated in each segment arising out of a Large

TCP Segment transmit operation.

Hardware IPv4 Post-DMA

Processing Enable

27 RW 0 Enable hardware processing of LSO IPv4 packets.

This bit has no effect on Post-DMA processing of

IPv6 packets. This bit is TCP Segmentation

Enable bit.

Note: LSO using jumbo frames is permissible on some Broadcom controllers (i.e., BCM5718). This is

accomplished by appropriately programming the MSS field of the Send BD.

Table 29: ISO Read DMA Mode Register (Offset: 0x4A00) (Cont.)

Name Bits Access

Default

Value

Description

0x4

0x8

0xC

Host Address

0x0

Length[15:0]

HdrLen[1:0] MSS[13:0]

Flags

VLAN Tag[15:0]

31 15 0

Loading...

Loading...