10h–1Fh Register Map Detailed DescriptionBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 536

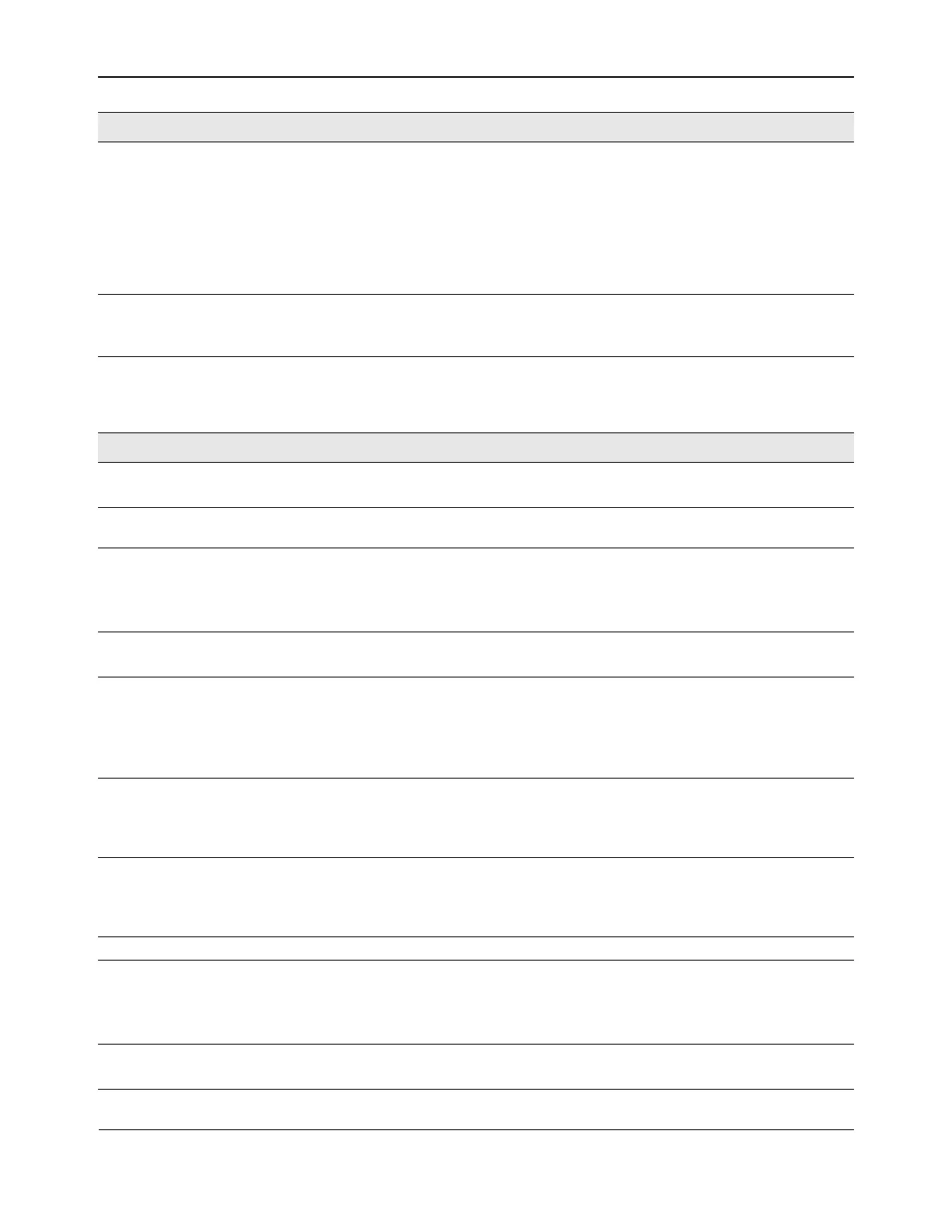

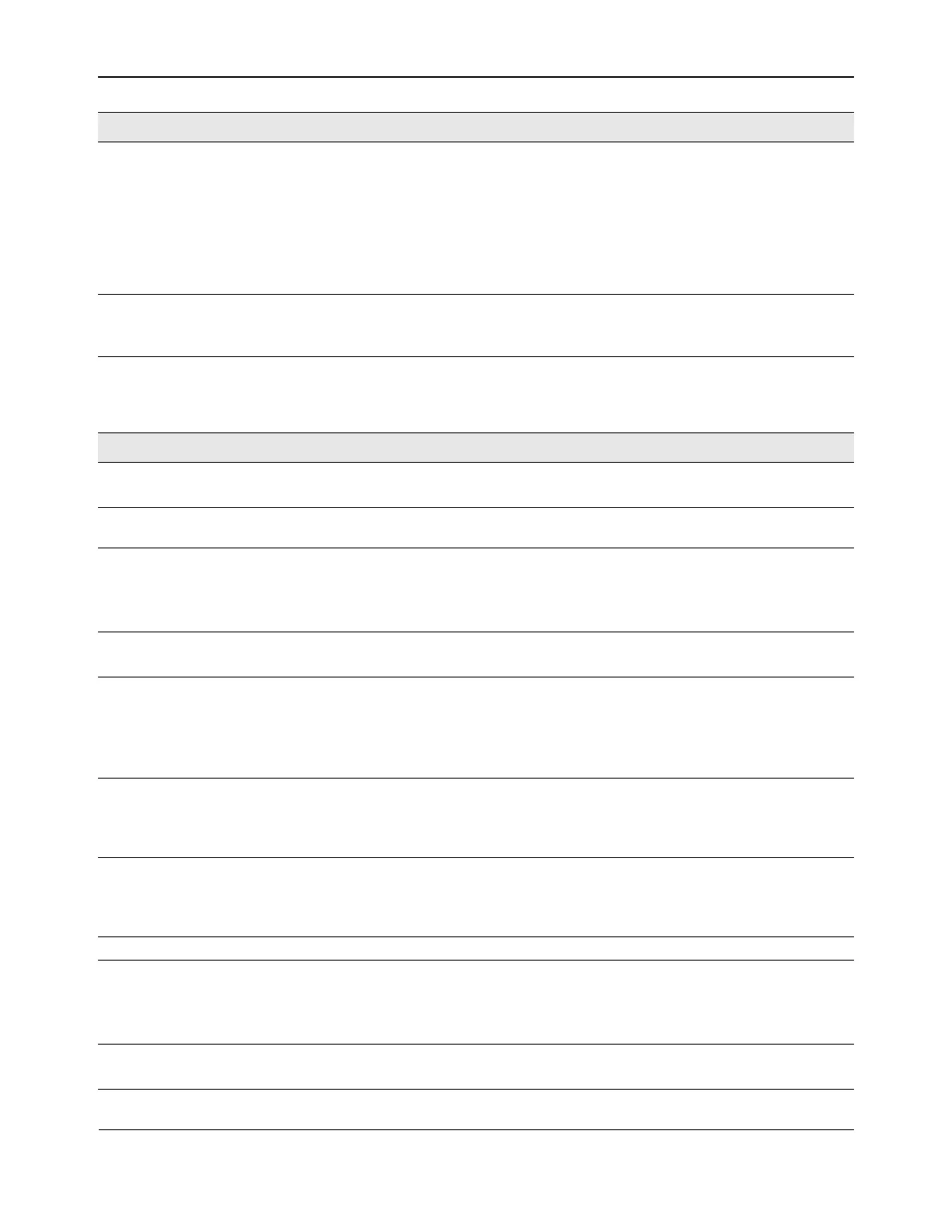

1Ch: Test 1000-X Register (Shadow Register Selector = “19h”)

1 SGMII 10/100 RX FIFO

FRE QUENCY LOCK

MODE

(forced high internally

when =>

sgmii_slave_mode and not

remote_lpbk)

RW 1 = SGMII RX FIFO will assume that the SerDes

recovered clock and the local clock are

frequency locked. This will essentially bypass

the FIFO with the lowest possible latency in 10/

100 speeds

(useful for applications where the MAC/switch

and PHY are using the same crystal)

0 = normal operation

0

0 AUTO-DETECT SGMII/

GBIC MODE

RW 1 = enable auto-detection between SGMII and

GBIC modes

0 = normal operation

0

Bit Name RW Description Default

15 WRITE ENABLE RW 1 = write bits [9:0]

0 = read bits [9:0]

0

14:10 SHADOW REGISTER

SELECTOR

RW Shadow Register Selector 11001

9 USE COPPER SPEED RW 1 = force dig1000x speed to copper speed

(used to test FIFOs in 10/100 mode from GMII

pins)

0 = normal operation

0

8 DLL BYPASS CLOCK

ENABLE

RW 1 = enable dll bypass clock (tpin 11)

0 = disable dll bypass clock

0

7 TX FIFO SGMII 10/100

EARLY PREAMBLE

MODE =>

towards SerDes link

partner

RW 1 = enable transmitting early preamble in SGMII

10/ 100 mode in order to reduce latency in half-

duplex.

(TX FIFO)

0 = normal operation

0

6 RX FIFO SGMII 10/100

EARLY PREAMBLE

MODE =>

towards copper link partner

RW 1 = enable transmitting early preamble in SGMII

10/ 100 mode in order to reduce latency in half-

duplex (RX FIFO).

0 = normal operation

0

5 BLOCK TXEN MODE

FOR dig1000x_tx_fifo =>

towards SerDes link

partner

RW 1 = block txen for 7 bytes after end of packet in

1000-X mode, 6.5 bytes in SGMII 10/100.

0 = normal operation

0

4 RESERVED RW write as 0, ignore on read 0

3 FORCE TXFIFO ON

(dig1000x_tx_fifo)

towards SerDes link

partner

RW 1 = force TXFIFO to be always active in 1000X

0 = normal operation

0

2 BYPASS PCS RECEIVE RW 1 = bypass pcs receive

0 = normal operation

0

Bit Name RW Description Default

Loading...

Loading...